#### **Quadra Solutions Limited**

People. Knowledge. Innovation.

# Save Time & Money with an Integrated Design Flow

For many years it has been acceptable to use individual point tools to analyse and verify your high speed layouts and critical nets, but today's high performance FPGAs, DSPs and Micro-Processors require a more sophisticated approach

The CADSTAR High Speed Design Suite lets you adopt an integrated design flow to create, implement, analyse, verify and document all of your constraints in one seamless environment

### Who cares about Integration?

- > You and your colleagues

- > Design, Layout, Production, Test

- > Fast, Accurate, Secure, Repeatable

- > Your Partners

- > Consultants, Fabrication, Assembly, Test

- > Accurate, Timely, Complete

- > Management

- > Internal, External (customers)

- > On schedule, to Budget

#### Why is Integration important?

- > Integration:

- Enables a single repository for all critical data in the design flow

- Eliminates the need for data translation between tools

- > Reduces risk and potential for error

- > Saves time!

### What data can you share?

- > Libraries

- > Electrical (Symbol, Component, Part)

- > Mechanical (3D)

- > Simulation & Modelling (Spice, IBIS, etc.)

- > Electronic Design Data

- > Schematic, PCB Layout, ReUse blocks, etc.

- > Rules & Constraints

- > Manufacturing, Electrical

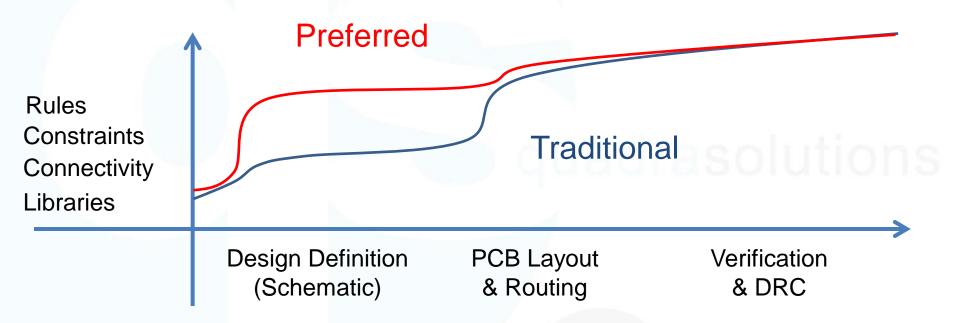

#### When is Data Required?

> Builds up during the design process

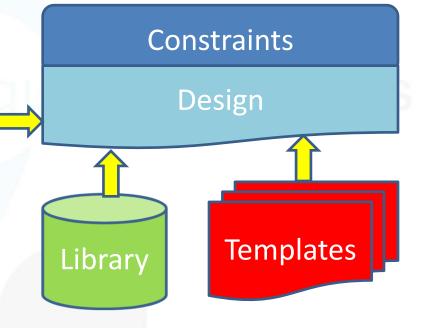

#### Where does the data reside?

- > Libraries

- > CAD Library or Database

- > Company, User, Project

- > Rules

- > Templates

- > Company, User, Project

- > Design Data

- > Project folder

- > Variants

- > Constraints

- > Constraints database

- > Linked to the design document

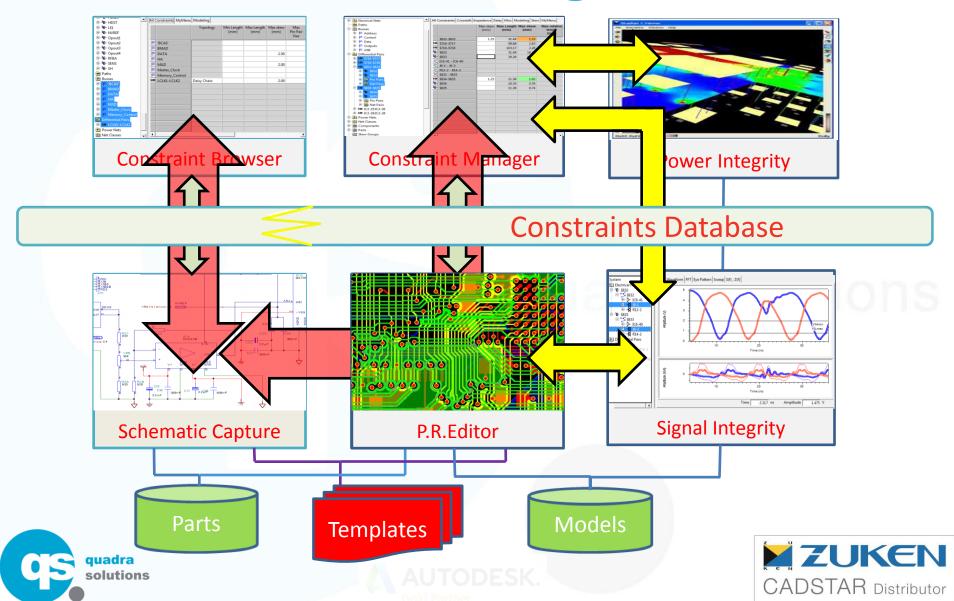

# How integration works in the CADSTAR design flow

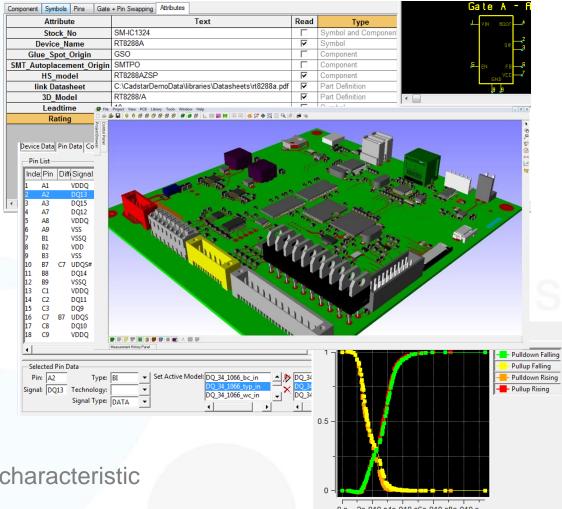

## Libraries

- > CAD

- > Electrical

- > Design

- > Selection

- > Data-centric

- > Information

- > Lifecycle

- > History

- > Versioning

- > Models

- > Simulation

- > Packaging

- > Pin types and characteristic

- > 3D

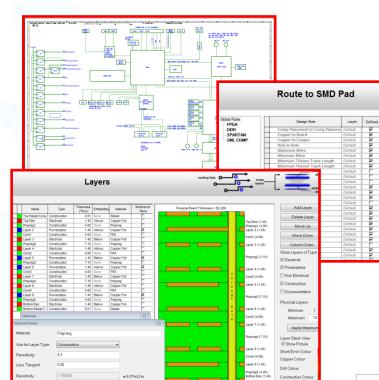

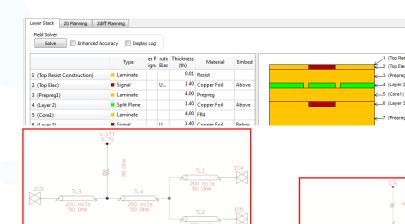

## **Templates**

- > Library creation

- > Symbols, Footprints, Documentation

- > Standards (Corporate, National, External)

- > Attributes

- > Schematic

- > Structure

- > Conventions

- > PCB

- > Layer Stack

- > Rules set

- > Manufacturing

Save DRC File

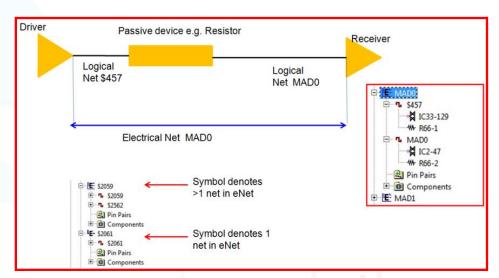

#### **Constraint Definition Process**

- > Automation

- > Net conversion from Logical to Electrical

- > Classification

- > Organisation

- > Organisation

- > Structure

- > Constraint Entry

- > Group

- > Net

- > Pin-Pair

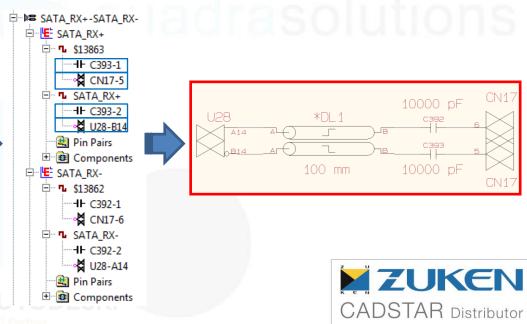

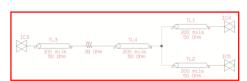

### **Automation - eNet Conversion**

- Concatenation of nets to include

- > terminators

- > Serial or Differential

- > exclude power connections

- > Pull up/down

- > filtering

quadra

solutions

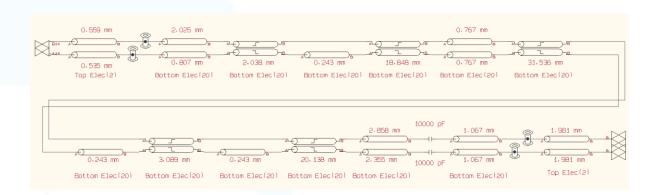

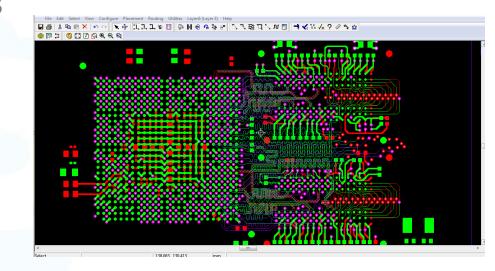

## eNet Physical Results - Example

> Results

> Topology

> Routing

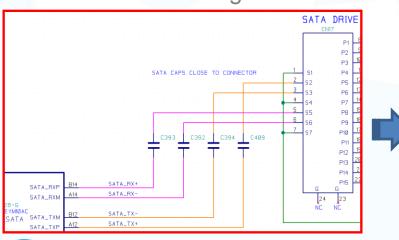

#### **High Speed Design - Engineering Process**

- Identify critical nets

- > Busses, Diff Pair, Clocks....

- Establish constraint values

- Datasheet, Calculation, Signal Integrity Verification, other

- > Implement net constraints

- > Length, Delay, Skew, Topology

- > Build constraint groups

- > Busses, Groups, Nets, Pins

- > Action Place & Route

- > To physical design rules

- > To Constraints

- Extend Analysis and Verification

- > Measure, analyse and simulate

- > HighSpeed Router

- > Signal Integrity

- > Power Integrity

- > 3D

- Document Results

- Verify conformance of the design to initial objectives

- > Statistics

- Reports

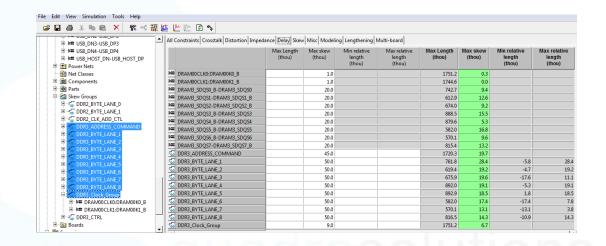

#### **Constraints - Classification**

- > Automatic extraction

- > Power Nets

- > Component Types & Values

- > Busses

- > Differential Pairs

| Electrical Nets                                   |     |                           |     |              | (thou) |

|---------------------------------------------------|-----|---------------------------|-----|--------------|--------|

| Paths                                             | )XE | DMI2_+TRX3-DMI2TRX3       | All | Daisy Chain  |        |

| Busses                                            | )#2 | DMI2_+TRX4-DMI2TRX4       | All | Daisy Chain  |        |

| Differential Pairs  Differential Pairs  Down Nets | )XE | DRAM00CLK0:DRAM00K0_B     | All | H-Tree       | 1      |

| Net Classes                                       | )#2 | DRAM00CLK1:DRAM00K1_B     | All | H-Tree       | 1      |

| ⊕ ® Components                                    | )E  | DRAM3_SDQS0_B-DRAM3_SDQS0 | All | Daisy Chain  | 20     |

| ⊕ ® Parts                                         | )E  | DRAM3_SDQS1-DRAM3_SDQS1_B | All | Daisy Chain  | 20     |

| E Skew Groups                                     | )E  | DRAM3_SDQS2-DRAM3_SDQS2_B | All | Daisy Chain  | 20     |

| Topologies                                        | )E  | DRAM3_SDQS3_B-DRAM3_SDQS3 | All | Daisy Chain  | 20     |

| A reference                                       | )E  | DRAM3_SDQS4_B-DRAM3_SDQS4 | All | Daisy Chain  | 20     |

|                                                   | N=  | DRAM3_SDQS5_B-DRAM3_SDQS5 | All | Daisy Chain  | 20     |

| `~_~`                                             | )E  | DRAM3_SDQS6_B-DRAM3_SDQS6 | All | Daisy Chain  | 20     |

|                                                   | )E  | DRAM3_SDQS7-DRAM3_SDQS7_B | All | Daisy Chain  | 20     |

|                                                   | NE  | HDMI TV CLVN HDMI TV CLVD | ΛII | Daisse Chain |        |

# **Constraints - Organisation**

- > Create structure in the design with:

- > Net Class

- > Bus

- > Sub-Bus

- > Diff Pair

- > Pin Pair

- > Path

| ⊕ <b>LE-</b> TXEN              |

|--------------------------------|

| ⊞ <b>IE-</b> TXERR             |

| Paths                          |

| D Busses                       |

| 🕩 📁 Address Bus A[0-24]        |

| ⊕- ► Control                   |

| 🖃 ⊨ Data_Bus_D[0-31]           |

| 🖶 🎏 SubBus1                    |

| . F SubBus2                    |

| . F SubBus3                    |

| ⊞   <b>E</b> SubBus4           |

| ⊕- <b>F</b> Outputs            |

|                                |

| 🖃 🖻 Differential Pairs         |

|                                |

|                                |

| ⊞ DA1_In-DB1_In                |

| ⊞ DA2_In-DB2_In                |

|                                |

| ⊞ BE Ethernet_TX+-Ethernet_TX- |

| 🗈 💼 Power Nets                 |

|                                |

|     |                           |     |             | () | (, | Vias | (01111) | (01111) |

|-----|---------------------------|-----|-------------|----|----|------|---------|---------|

| ):E | D2+-D2-                   | All | Daisy Chain |    |    |      | 63      | 77      |

| E   | D1+-D1-                   | All | Daisy Chain |    |    |      | 63      | 77      |

| æ   | DA1_In-DB1_In             | All | Daisy Chain |    |    |      | 63      | 77      |

| E   | DA2_In-DB2_In             | All | Daisy Chain |    |    |      | 63      | 77      |

| ×   | Ethernet_RX+-Ethernet_RX- | All | Daisy Chain |    |    |      | 63      | 77      |

| E   | Ethernet_TX+-Ethernet_TX- | All | Daisy Chain |    |    |      | 63      | 77      |

| F   | Address Bus A[0-24]       | All |             |    |    |      | 63      | 77      |

|     | Control                   | All |             |    |    |      | 63      | 77      |

| F   | Data_Bus_D[0-31]          | All |             |    |    |      | 63      | 77      |

| F   | Outputs                   | All |             |    |    |      | 63      | 77      |

| F   | USB                       | All |             |    |    |      | 63      | 77      |

| F   | SubBus1                   | All |             |    |    |      | 63      | 7       |

| F   | SubBus2                   | All |             |    |    |      | 63      | 7       |

| F   | SubBus3                   | All |             |    |    |      | 63      | 77      |

| F   | SubBus4                   | All |             |    |    |      | 63      | 77      |

|     |                           |     |             |    |    |      |         |         |

|     |                           |     |             |    |    |      |         |         |

|     |                           |     |             |    |    |      |         |         |

|     |                           |     |             |    |    |      |         |         |

# Constraint – Assigning Values

- > Topology

- > Impedance Profile

- > Skew Groups

- > Simple

- > Relative

- > Intra-Net Skew

- > Virtual Branch Point

- > Length v. Delay Mode

|                  | Туре        | wiath<br>(th) | (Ohm) | velocity<br>(th/ps) |                  | Туре   | (th) | (th) | (Ohm) | (Ohm) | (Ohm)  |

|------------------|-------------|---------------|-------|---------------------|------------------|--------|------|------|-------|-------|--------|

| All              |             | 4.00          |       |                     | All              |        | 4.00 | 4.00 |       |       |        |

| 2 (Top Elec)     | Signal      |               | 58.69 | 6.38                | 2 (Top Elec)     | Signal |      |      | 89.11 | 44.55 | 71.12  |

| 4 (Layer 2)      | Split Plane |               | 98.85 | 6.12                | 4 (Layer 2)      | Split  |      |      | 90.06 | 45.03 | 148.50 |

| 6 (Layer 3)      | Signal      |               | 49.38 | 5.69                | 6 (Layer 3)      | Signal |      |      | 76.56 | 38.28 | 59.09  |

| 8 (Layer 4)      | Signal      |               | 49.38 | 5.69                | 8 (Layer 4)      | Signal |      |      | 76.56 | 38.28 | 59.09  |

| 10 (Layer 5)     | Split Plane |               | 62.80 | 5.69                | 10 (Layer 5)     | Split  |      |      | 83.83 | 41.91 | 81.39  |

| 12 (Layer 6)     | Split Plane |               | 62.80 | 5.69                | 12 (Layer 6)     | Split  |      |      | 83.83 | 41.92 | 81.39  |

| 14 (Layer 7)     | Signal      |               | 49.38 | 5.69                | 14 (Layer 7)     | Signal |      |      | 76.56 | 38.28 | 59.09  |

| 16 (Layer 8)     | Signal      |               | 49.38 | 5.69                | 16 (Layer 8)     | Signal |      |      | 76.56 | 38.28 | 59.09  |

| 18 (Layer 9)     | Split Plane |               | 98.85 | 6.12                | 18 (Layer 9)     | Split  |      |      | 90.06 | 45.03 | 148.50 |

| 20 (Bottom Elec) | Signal      |               | 58.69 | 6.38                | 20 (Bottom Elec) | Signal |      |      | 89.11 | 44.55 | 71.12  |

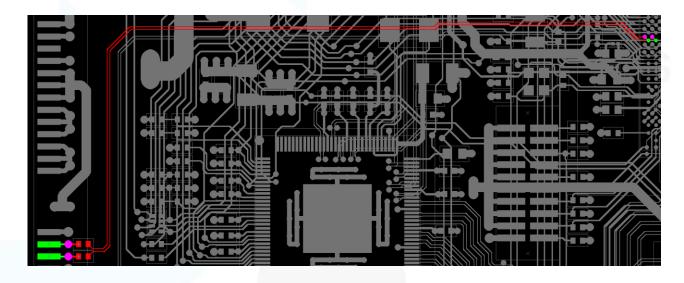

## **Constraint Implementation**

- > Place and Route

- > Dynamic DRC

- > Clearance

- > Length

- > Delay

#### **Constraint Verification**

- > Dynamic

- > Length / Delay markers

- > Pop-up

- > Signal Integrity

- > Power Integrity

- > EMC

- > Power distribution

- > Decoupling

#### **Constraint Documentation**

- > Spreadsheet

- > Reports

- > DRC

- > Skew

- > Length

- > Delay

- > Embed links in Schematic and PCB

## **Benefits of Integration - summary**

- > For you and your colleagues

- > Design, Layout, Production, Test

- > Fast, Accurate, Secure, Repeatable

- > For your partners

- > Consultants, Fabrication, Assembly, Test

- > Accurate, Timely, Complete

- > For your management

- > Internal, External (customers)

- > On schedule, to Budget

### **Quadra Solutions Limited**

People. Knowledge. Innovation.