# High-performance embedded systems

Presenter

Hans Klos

Introduction Sintecs

- Trends that make Electronic designs complex

- Electronic Design Challenges

- High-Speed Board Analysis

# **The Company Sintecs**

Core competences in electronic development, (embedded) software development and design analysis & verification

### ાર્ક Freescale Proven Partner

- System on Module development

- Freescale i.MX processor family

- Freescale QorlQ processor family

- Custom electronic development

- Integrate module in customer design

# Trends that make Electronic designs complex

### **Trends**

www.sintecs.eu

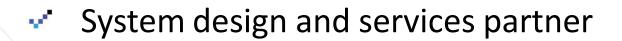

- Shorter Rise & fall time

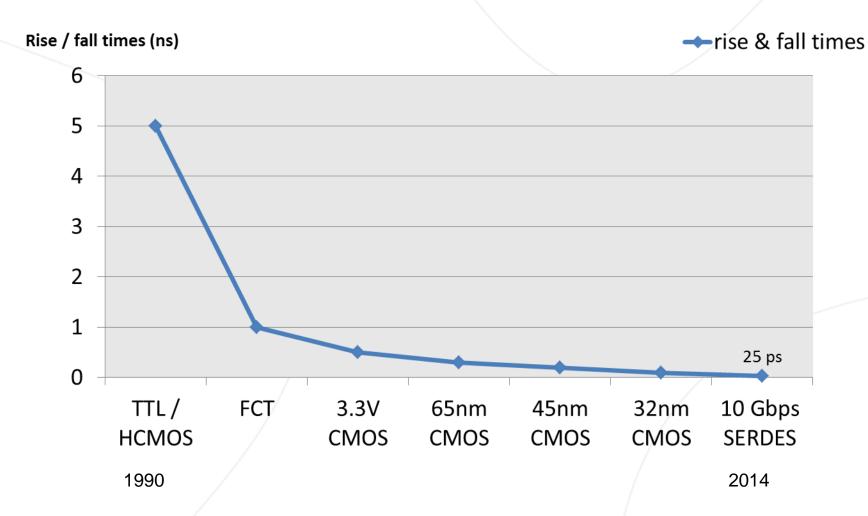

- Increasing Data Rate & Bandwidth

- Lower power supply voltage

- Higher currents

- Dense & larger pin count devices / smaller pitch

### Rise & Fall times

## **Increasing Data Rate**

## Challenges

- Fast switching devices

- Packages

- Device loading

- Number of power rails

- Multi Gigabit signaling

### Rise & Fall times

# Routing challenges

### DDR3 routing guidelines for a Xilinx Kintex 7

Match within a byte lane all the DQ, DM and DQS within 5ps → within less than 1 mm

- The maximum electrical delay between any DQ and its associated DQS/DQS# should be ±5 ps.

- The maximum electrical delay between any address and control signals and the corresponding CK/CK# should be ±25 ps.

- The maximum electrical delay of any DQS/DQS# should be less than that of CK/CK#.

#### DDRx timing simulation needed!

## **Packages**

#### Example from the Xilinx Kintex 7 datasheet

Table 50: Package Skew

| Symbol               | Description                 | Device   | Package | Value | Units |

|----------------------|-----------------------------|----------|---------|-------|-------|

| T <sub>PKGSKEW</sub> | Package Skew <sup>(1)</sup> | XC7K70T  | FBG484  | 108   | ps    |

|                      |                             |          | FBG676  | 135   | ps    |

|                      |                             | XC7K160T | FBG484  | 118   | ps    |

|                      |                             |          | FBG676  | 136   | ps    |

|                      |                             |          | FFG676  | 161   | ps    |

|                      |                             | XC7K325T | FBG676  | 146   | ps    |

|                      |                             |          | FFG676  | 154   | ps    |

|                      |                             |          | FBG900  | 163   | ps    |

|                      |                             |          | FFG900  | 161   | ps    |

|                      |                             | XC7K355T | FFG901  | 149   | ps    |

|                      |                             | XC7K410T | FBG676  | 165   | ps    |

|                      |                             |          | FFG676  | 168   | ps    |

|                      |                             |          | FBG900  | 151   | ps    |

|                      |                             |          | FFG900  | 146   | ps    |

|                      |                             | XC7K420T | FFG901  | 149   | ps    |

|                      |                             |          | FFG1156 | 145   | ps    |

|                      |                             | XC7K480T | FFG901  | 149   | ps    |

|                      |                             |          | FFG1156 | 145   | ps    |

168ps worst case package skew ~ 20 mm

#### Notes

- These values represent the worst-case skew between any two SelectIO resources in the package: shortest delay to longest delay from die pad to ball.

- 2. Package delay information is available for these device/package combinations. This information can be used to deskew the package.

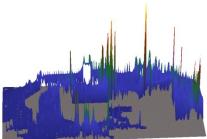

### Number of Power Rails / Area fills

- Number of Power Rails / Area fills

- Small pitch BGA's

Planes are not low impedance

any more

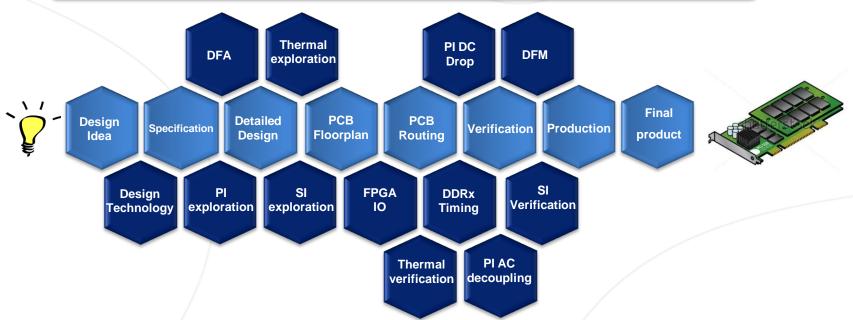

# High-speed board analysis

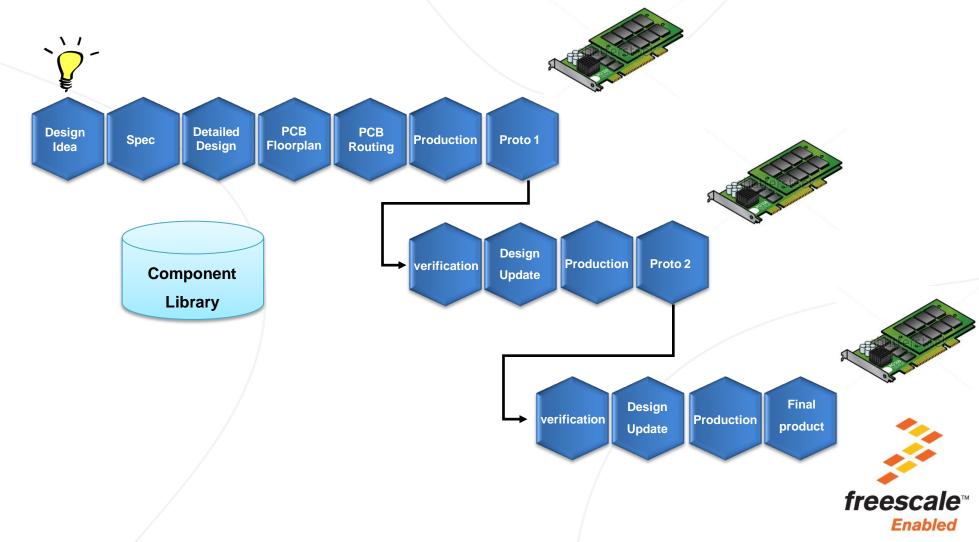

### Traditional electronic design flow

### **High-speed board analysis**

#### Signal Integrity

Power Integrity

#### **Thermal**

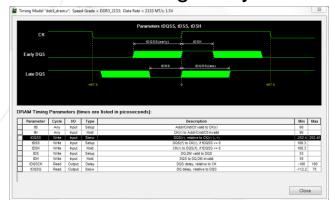

#### DDRx timing analysis

#### **DRC**

## High-speed design flow

#### **Component database:**

Schematic symbols | Footprints | Simulation models (SI /PI / Thermal / Timing)

#### **Design Constraints**

PCB Technology | Electrical constraints | Physical constraints

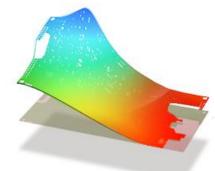

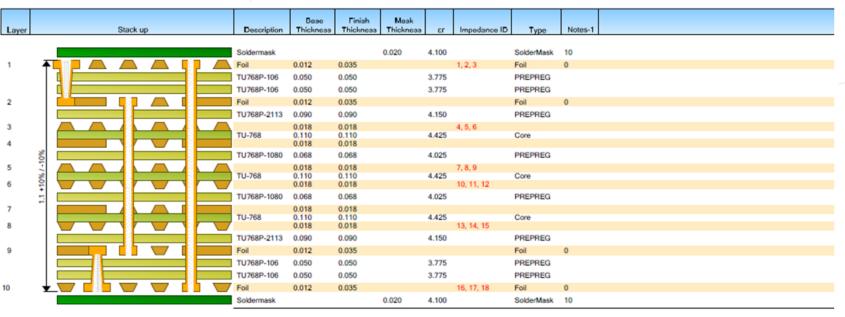

## Design technology setup

- Explore which impedances are needed on the board

- How many signal and power planes are needed

- What is smallest pitch of BGA's

- How many power rails?

Dielectric Thickness = 0.846 | Solder Mask Thickness = 0.040 | Stack Up Thickness = 1.093 | Stack Up Thickness with Solder Mask = 1.133 |

www.sintecs.eu

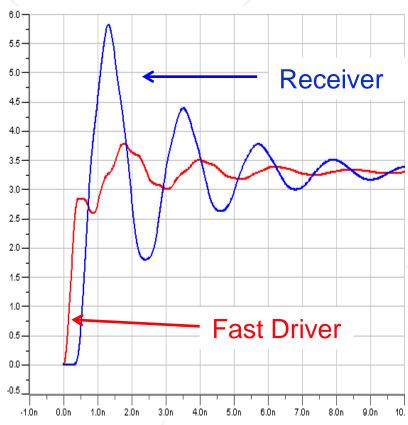

# **Signal Integrity**

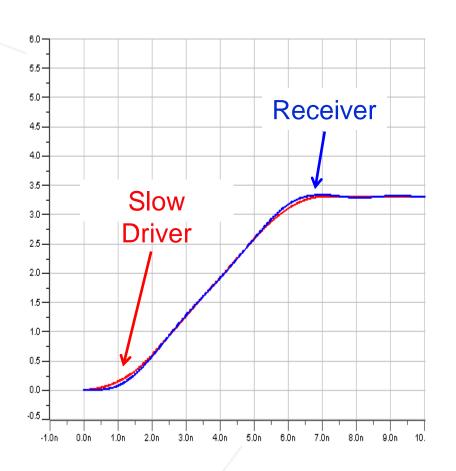

- Signal over/undershoot

- Trace impedances

- Eye Pattern / Mask

- Crosstalk

- Monotonic signals

Adjust Mask

Copy to Clip.

Erase

Print\_

Close

2,000 ÷ ns

Five mask

Position

-20 -V

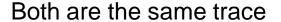

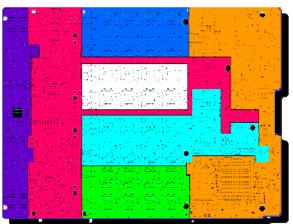

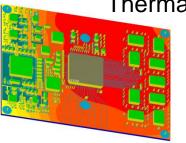

## **Power Integrity**

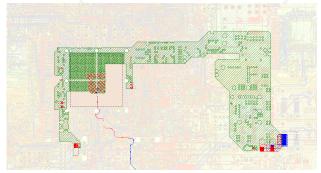

#### **DC** analysis

Voltage drop

**Current densities**

DC DROP CURRENT DENSITY

Design file: "D\Sh\rho\si\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\kiles\rightar\

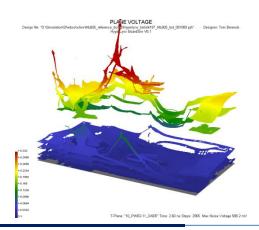

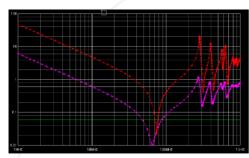

### **AC** analysis

decoupling / Target impedance

Plane noise

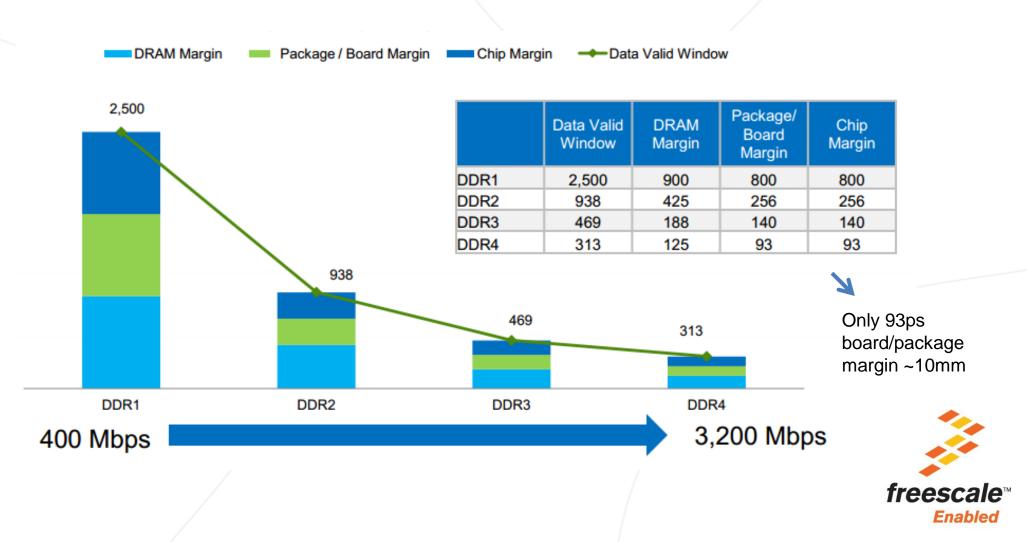

# **DDRx** timing

# **DDRx timing margins**

# Design Rule Checks

- Trace crossing gaps

- IO coupling

- IC's over split

- Traces near plane edge

- Decoupling placement

- Power/Ground width

- Long nets

- 🕶 .../.

### Summary

- A good high-speed design starts with understanding of different hiigh-speed effects which can have impact on your design

- Try to develop first-time right

- ✓ When you plan 2 proto types, you will get 2 proto types

- Make use of high-speed board analysis tools

# Thank you!

Hans Klos Sintecs BV

hans.klos@sintecs.eu

www.sintecs.eu

Sintecs BV Lansinkesweg 4 7553 AE Hengelo Tel. +31(0)742555713 Fax. +31(0)742555780