### TRENDS IN ESD PROTECTION OF AUTOMOTIVE IC'S

### DESIGN, STANDARDS & BEYOND

**BART HUITSING**

ESD PRAKTIJKDAG 4 NOVEMBER 2014

SECURE CONNECTIONS FOR A SMARTER WORLD

### **Presentation outline**

- Introduction

- Component level ESD standards

- Automotive ESD standards

- System level ESD & beyond

- On-chip ESD protection design

- Summary

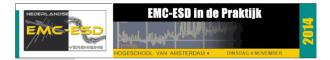

#### Introduction

- This is a presentation about ESD standards for electronic components for the Automotive Industry

- Automotive industry have high demanding requirements

- High reliability

- Safety regulations

- Hostile environment

- Low return rate requirement

- Long life-span

- Semiconductor footprint for automotive is ever growing

- ESD is a key design parameter to quantify robustness

### **NXP** supplies automotive industry

### COMPONENT LEVEL ESD STANDARDS

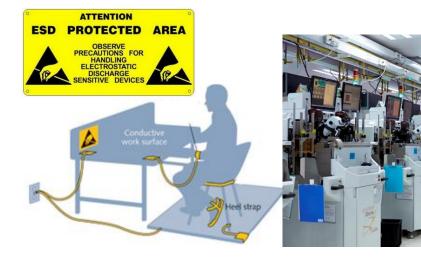

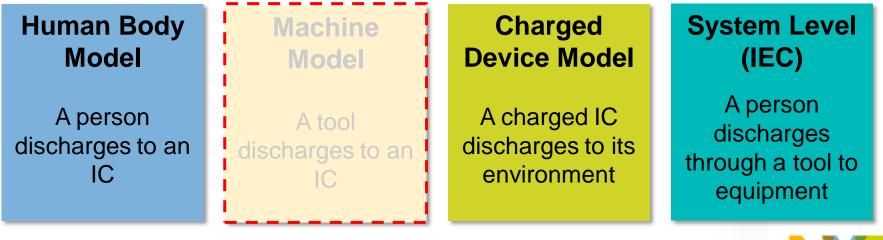

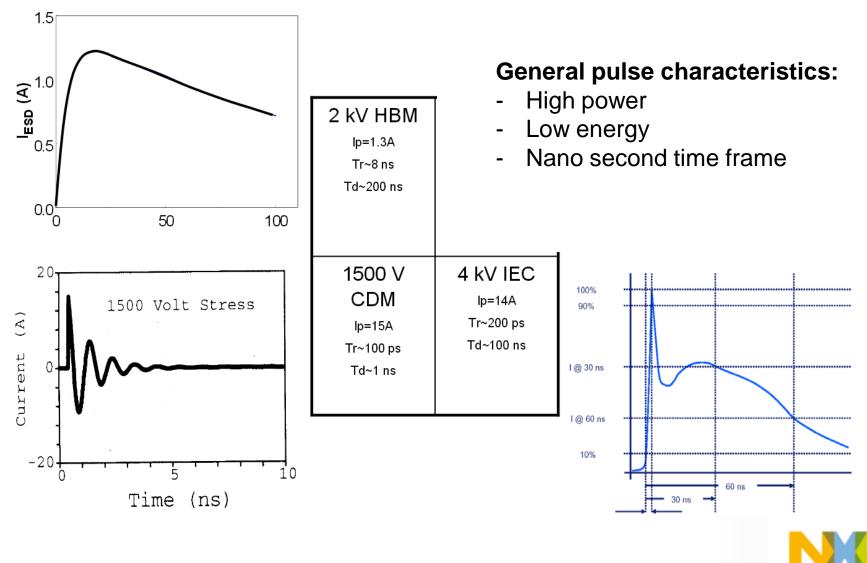

### Two worlds of ESD

#### **Component level**

- Semiconductor parts

- Handling in ESD controlled environment

- High currents, low energy

#### **System level**

- Modules, system boards and complete products

- ESD uncontrolled environments

- Higher currents, higher but still low energy

### **Testing ESD susceptibility**

- Standards:

- Classification: Test results in pass/fail for a given level

- Each standard covers a limited part or real-life ESD

- To have reproducible results

- Describe the waveform and test procedure

- In general, semiconductor components are qualified according these standards that address different situations:

Ref [1] ... [7]

### **Phase out of Machine Model**

| JESD22-115C (Nov 2010)                                                                                                               | ANSI/ESD S5.2 > STM5.2                                                                                                                    |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| <ul> <li>"Classification testing" renam</li> </ul>                                                                                   | • ANSI standard S5.2 has been                                                                                                             |  |  |  |

| to "Cha                                                                                                                              | tandard                                                                                                                                   |  |  |  |

| <ul> <li>"[]]</li> <li>Observed fail</li> <li>ocrrelated to</li> <li>occur at a</li> <li>qual</li> <li>Only</li> <li>nece</li> </ul> | <pre>hotivation: ures for MM are strongly HBM results. They only lower stress voltage.  M yields no added value ly increases cost. </pre> |  |  |  |

| ESD Qualification"                                                                                                                   |                                                                                                                                           |  |  |  |

### **ESD Standard pulses compared**

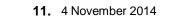

### AUTOMOTIVE ESD STANDARDS

### **Automotive industry**

- Demanding requirements

- Hostile environment

- Low return rate requirement

- Long life-span

- ... for niche market!

- The Automotive Electronics Council (AEC)

- Issues common qualification specifications for electronics for the automotive industry

- Lead standard: AEC-Q100 (Stress Qualification for IC's)

- ESD and Overstress

- Life test

- Originally established in by Ford, Chrysler and GM in early 90's

- NXP is Technical Committee Member since

2005

Anatomy of AEC-Q100 Rev G (ESD only)

### **Recent developments in AEC-Q100**

- AEC-Q100 Rev H is to be released soon:

- Ballot passed Sept/Oct 2014

- MM standard is removed

- Intention to follow ANSI/ESDA/Jedec JS-002 for CDM

- ANSI/ESDA/Jedec JS-002 (CDM)

- Second joint standard between ESD Association and Jedec

- Merge of JESD22-C101 and ANSI/ESD S5.3.1

- Focus on backward compatibility

- Change from voltage level defined to current level defined stress

| Organiza | ation | Previous step | Next step                      |

|----------|-------|---------------|--------------------------------|

| ESDA     |       | Accepted      | Industry review                |

| Jedec    | JEDEC | Ballot passed | Approval by Board of Directors |

## SYSTEM LEVEL ESD & BEYOND

### System Level ESD

- No AEC standard because AEC is component level only

- Still, more and more customers require a component to PASS a system level requirements

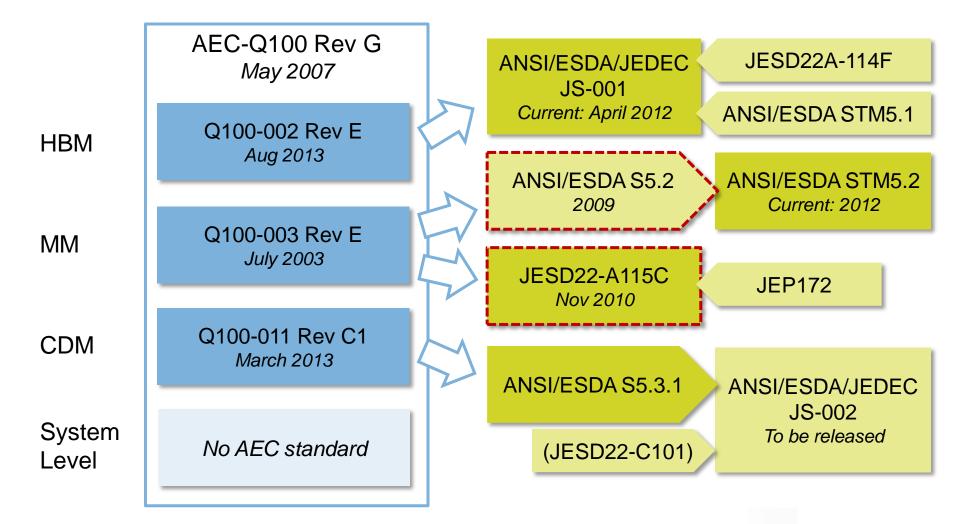

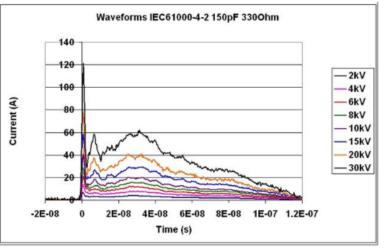

- System level standard IEC-61000-4-2

- ANSI ESD SP 5.6 (Human Metal Model) for IC components

Figure 5: Measured waveforms of contact discharge from an IEC 61000-4-2 ESD gun on the prescribed calibration

### **Other standards**

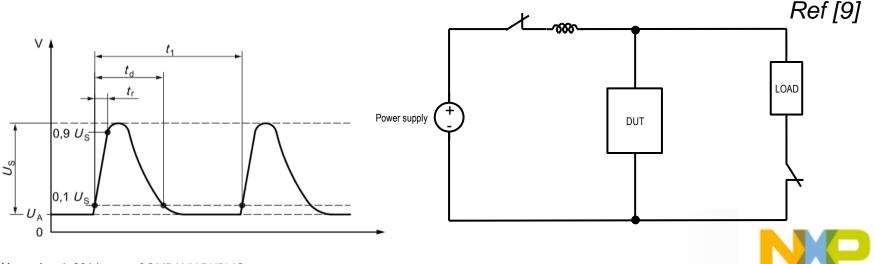

- ISO7637-2: Electrical disturbances from conduction and coupling

- System level standard

- Discharge / overvoltage due to change in inductive load on the wiring loom

- Voltage spikes up to 112Volts, duration of <u>50us</u> (250x longer than HBM!)

- No ESD test, but EOS test!

# ON-CHIP ESD PROTECTION

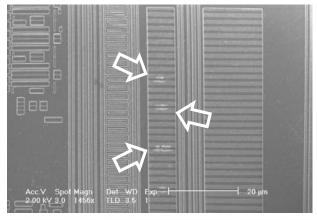

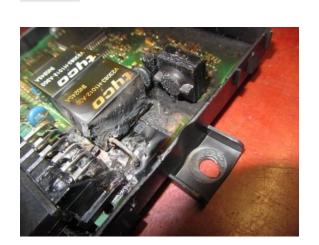

### **Design for ESD robustness**

- Mask sets are expensive, therefore a first-time right is eminent!

- Development of an ESD protection strategy

- Semiconductor process knowledge

- What can go wrong (blow-up, melt, etc)?

- How can we prevent that?

- Create protection infrastructure

- CAD tools

- Simulation methods (2d simulation and/or SPICE based simulation)

- Design verification checks. Using Programmable Electrical Rule Checksets (PERC), critical circuit topologies may be identified

- Manual review

- Of schematic

- Of physical layout design

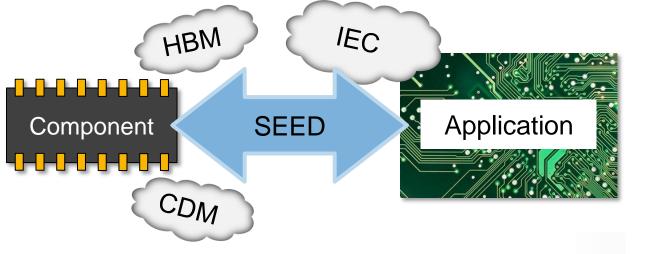

# System-efficient ESD Design (SEED)

- Component level ESD does not correlate to system ESD pulses

- High HBM levels do not guarantee a ESD-safe system design, but may limit IO performance

- Understand which magnitude of stress actually arrives on the IO pin in a system application.

NP

Ref [8]

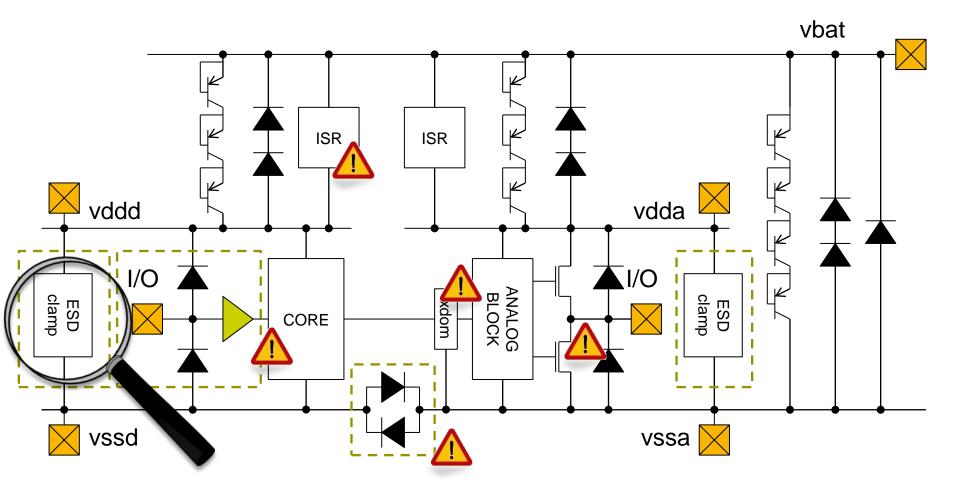

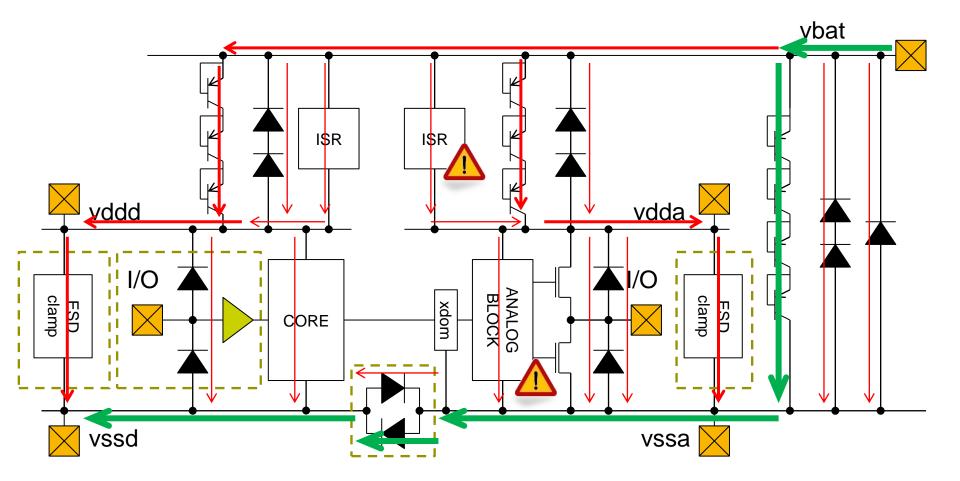

### Semi-automatic circuit analysis

Not a real product. Illustration purpose only.

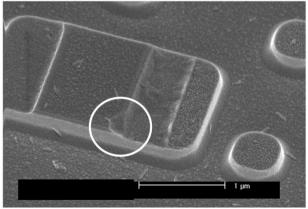

### **On-chip ESD simulation**

Not a real product. Illustration purpose only.

### Summary

- Because the Automotive industry has high demands, design for ESD is a significant effort

- Overview of the AEC-Q100 standard is given

- Some important (expected) changes

- Expected removal of Machine Model from AEC-Q100

- Alignment with the soon to be released JS-002 for CDM

- For ESD robustness, engineering takes place on multiple levels

- Device engineering, strategy development, codesign and troubleshooting

- Usage of dedicated CAD tools

- ... to have a first-time right design cycle!

## **THANK YOU!**

## **QUESTIONS?**

#### References

- ANSI ESDA/JEDEC JS-001, Electrostatic Discharge Sensitivity Testing Human Body Model (HBM) -Component Level

- ANSI ESD S5.3.1, Electrostatic Discharge Sensitivity Testing Charged Device Model (CDM) -Component Level

- 3. Jedec JESD22-C101, Field-induced Charged-Device Model Test Method For Electrostatic-Discharge-Withstand Thresholds Of Microelectronic Components

- 4. ANSI ESD STM5.2, Electrostatic Discharge Sensitivity Testing Machine Model (MM) Component Level

- 5. Jedec JESD22-A115, Electrostatic Discharge (ESD) SENSITIVITY Testing, Machine Model (MM)

- IEC61000-4-2 Electromagnetic Compatibility (EMC) Part 4-2: Testing And Measurement Techniques

Electrostatic Discharge Immunity Test

- 7. ANSI ESD SP5.6, Human Metal Model (HMM) Component Level

- 8. ESDA Industry Council on ESD Target Levels, White Paper 3: System Level ESD

- 9. ISO 7637-2:2011 Road vehicles Electrical Disturbances from conduction and coupling (Part 2)

### **Useful links**

- ESD Association <u>www.esda.org</u>

- Jedec <u>www.jedec.org</u>

- American National Standards Institute <u>www.ansi.org</u>

- Automotive Electronics Council

<u>www.aecouncil.com</u>

- NXP

www.nxp.com

### SECURE CONNECTIONS FOR A SMARTER WORLD