### Wearables & IOT – The next challenge

Yu-Chih Chen, Christine Toh 2<sup>nd</sup> June 2015

#### Outline

- Introduction

- Aesthetics and Packaging

- Battery Life and Power Consumption

- Security

- Summary

Cambridge Silicon Radio – "15 years delivering low power solutions to the consumer and automotive markets."

## **Five Platforms for Growth**

#### **Segments**

#### **Peripherals**

- Fixed Purpose

- Always ON, targeted experience

- Connectivity : BT/BTLE

- Battery Life : ~7days

- RTOS based

- Architecture-ARM Cortex-M

- Highly integrated signal processing

#### Wearable computing devices

- Multipurpose

- High Performance/rich user experience

- Drive for memory requirements

- Multimedia Rich graphics, audio etc.

- Battery Life : Everyday

- Multiple connectivity

- Full OS

- Architecture ARM Cortex-A9

- Highly integrated SOCs

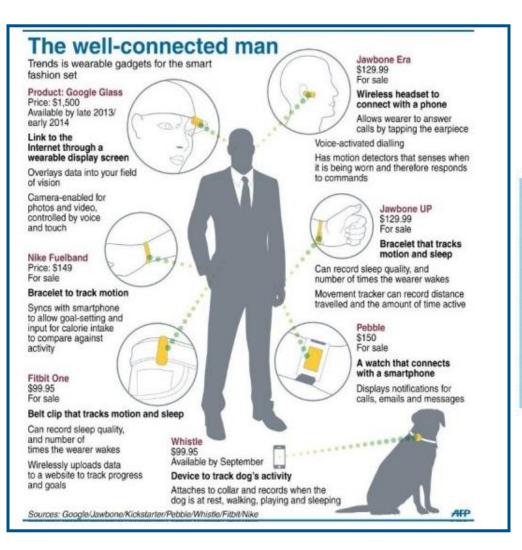

#### The Well Connected Man [& Woman ©]

#### Wearable Computing Device Shipments by Category (Millions)

|                             |         | 2013  | 2014  | 2015   |

|-----------------------------|---------|-------|-------|--------|

| Wearable Cameras            |         | 6.64  | 13.61 | 15.81  |

| Smart Glasses               |         | 0.01  | 2.13  | 10.57  |

| Smart Watches               |         | 1.23  | 7.44  | 24.92  |

| Healthcare                  |         | 13.45 | 22.59 | 34.25  |

| Sports/Activity Trackers    |         | 32.46 | 42.64 | 57.42  |

| Wearable 3D Motion Trackers |         | N/A   | 0.87  | 2.00   |

| Smart Clothing              | 4       | 0.03  | 0.72  | 1.24   |

|                             | Totals: | 53.90 | 90.00 | 164.20 |

|                             |         |       |       |        |

Source: Data from ABI Research World Market Forecast: 2013 to 2019

CSR

Right mix of Performance requirements for wearables

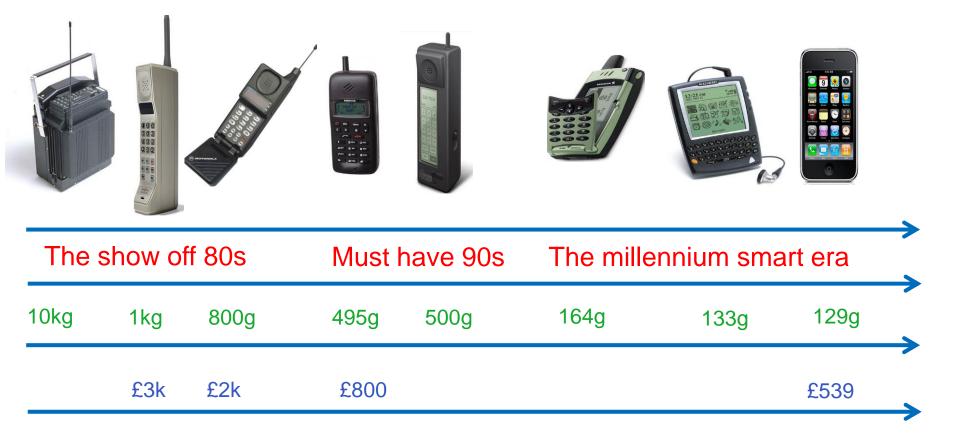

# An example: MOBILE PHONE EVOLUTION CSR

# Wearables usage and design considerations

2/3/4 JUNI 2015 JAARBEURS L

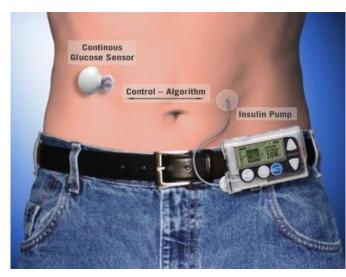

#### User Usage

- 24/7

- Environment used in

- Wearables close to body

- Constantly ON

- Privacy protection

Design factors to consider

- Small form factor-sleek , thin, light

- Thermal aspect need to be comfortable to the body

- Power management

- Privacy/security measures

# Aesthetic Appeal & Packaging-IF IT'S UGLY IT IS NOT WEARABLE

#### **CSR**

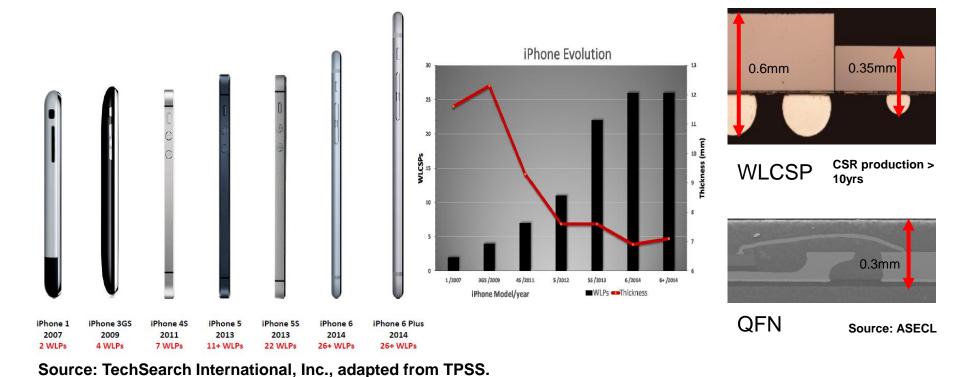

### Package Technology

- Component package

- Thickness and footprint

- MEMS & Sensor package

- One device, One process, One product

- Package technology primarily dominate the final body size

- System in Package

- Integration of above two package

#### Confidential © Cambridge Silicon Radio Limited 2015

#### **Component Package**

Thin package technologies

– WLCSP, QFN

ELECTRONICS & AUTOMATION 2/3/4 JUNI 2015 JAARBEURS UTRECHT

- Small footprint package technologies

- Higher "Silicon density" in the package (die size/package size)

- Example of silicon density

- WLCSP = 1

- CSP package = 0.8 ~ 1

- 2 dies stack CSP package = 1.6 ~ 2

Memory die stack on top of process

Samsung's 8 Flash die stack

Samsung's 3D STV technology

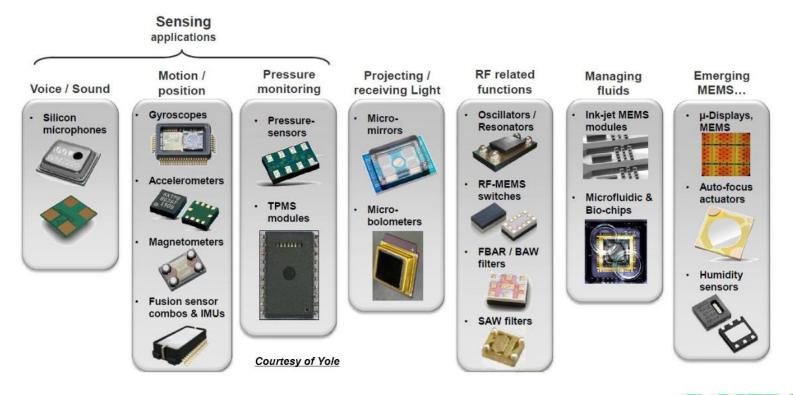

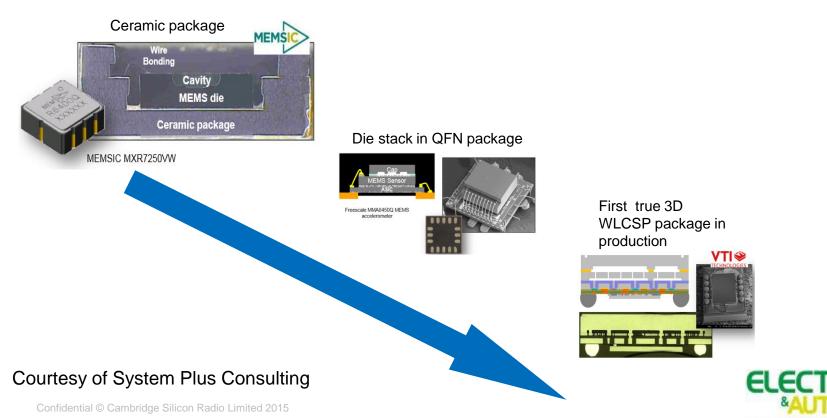

#### **MEMS & Sensor Package**

- Diversified & non-standardized package solution required

- Problem: "One device, One process, One product"

ELECTRONICS & AUTOMATION 2/3/4 JUNI 2015 JAARBEURS UTRECHT

#### **MEMS & Sensor Package**

Package technology primarily dominate the final body size

Ex: Accelerometer package size reduction

2/3/4 JUNI 2015 JAARBEURS UTRECH

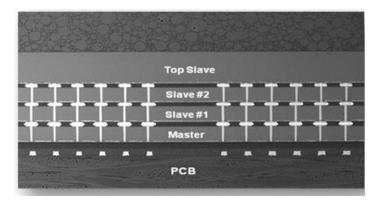

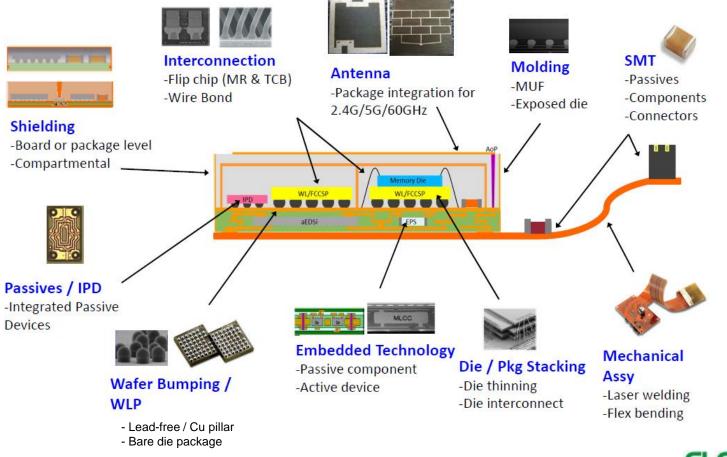

### **System in Package**

#### **CSR**

#### Enabling technologies

Courtesy of ASE

2/3/4 JUNI 2015 JAARBEU

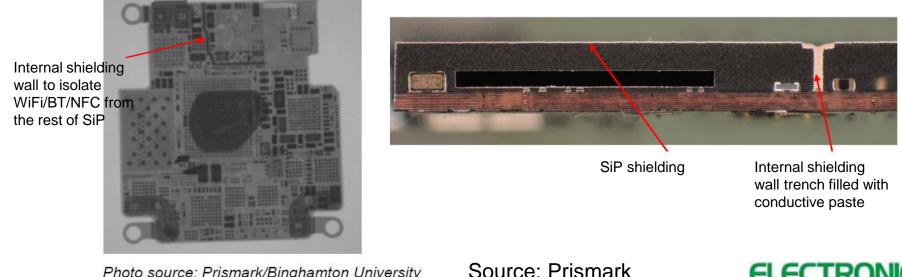

- EX: Apple Watch S1 SiP

- 8 layers microvia substrate with 50um L/S, and 360um thickness

- Many packages, primarily CSP and numerous passives

- All have a mounted height of 400um or less

- Advanced EMI shielding technology to reduce the SiP body size

- The entire package mounted height is 550um

Photo source: Prismark/Binghamton University

- Components drivers are form factor and height

- Same careabouts in MEMS technology with the additional challenge that there are multiple package types

- A great variety of SIP offerings but these are likely to shrink as the market matures and finds its way

- The backstory to all of these is the cost curve

- This will come from volume and never "reinventing the wheel"

#### Battery Life & Power consumption

- RF connectivity during ON state are always power hungry

- Increased demand in memory space on chip (ie more RAM) give burden on batteries life

- Always ON sensors and display units consume lots of power

- Battery technology didn't evolve as quickly as we like to ...

SO?

### THE NEED FOR BATTERY AND CHARGING INNOVATION

2/3/4 JUNI 2015 JAARBEURS UTRECH

- Today: Li-Ion technology. The battery size ~50% of the total footprint today.

- Density/capacity of battery ~ 300mAH. Restricted density. Need constant charging for high end wearables – user experience compromised

- New technology in batteries?

- Silicone Anode

- Ge nonowire

- Carbon flouride-for LP

application wearables

- Today: Wired Micro USB charger

- New technology in charging?

- RF wireless energy harvesting

- Photovoltaic

Don't expect changes to battery and charging technology overnight..... So can we do something innovative from design aspect of component level?

- Clever radio architecture can significantly reduce the active power

- Reduce the operational voltage of the system

- Operate as many blocks as possible at a lower voltage

- An integrated power supply is needed so that the voltage can be dynamically adjusted

- Frequency reduction

- Operate the chip at lower frequencies, gives a linear reduction in dynamic power

- Use transistors with lowest available leakage in the process

- Avoid external components that waste power

- External Li-Ion regulators for example reduce overall system efficiency

- etc.

#### This section focuses on Process Technology Improvements

#### CSR

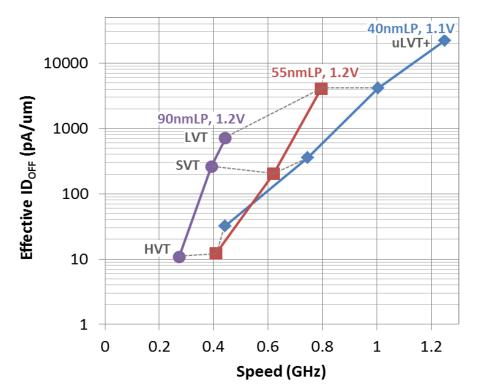

#### **Transistor Leakage Across Nodes**

- Advanced CMOS transistors are optimized for higher speed and lower active power but the lowest achievable leakage is usually higher than the previous node

- Battery life is key for BT Smart as chips spend much time in standby, making leakage reduction essential

- 40ULP was conceived based on the requirements

ELECTRONICS & AUTOMATION 2/3/4 JUNI 2015 JAARBEURS UTRECHT

#### **CSR**

#### **Pocket or Halo Implants**

- Pocket or Halo implants are used to control the transistor threshold voltage, Vt

- They are implanted at a steep angle (37 to 45 degrees) to get dopant under the polysilicon gate

- They are key to improving the transistor off state performance whilst not compromising its performance when turned on

| l <sub>OFF</sub><br>(pA/um) | 55LP<br>1.2V<br>(C60) | 40LP<br>1.1V<br>(C50) | 40ULP<br>1.1V<br>(C50) |

|-----------------------------|-----------------------|-----------------------|------------------------|

| NMOS                        | 24                    | 33                    | 11                     |

| PMOS                        | 4.4                   | 9                     | 4                      |

- 40ULP will achieve lower off-state leakage than 55LP

- VDD reduction is the only way to further reduce standby power

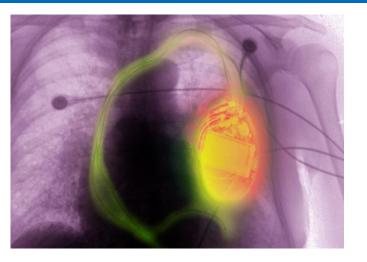

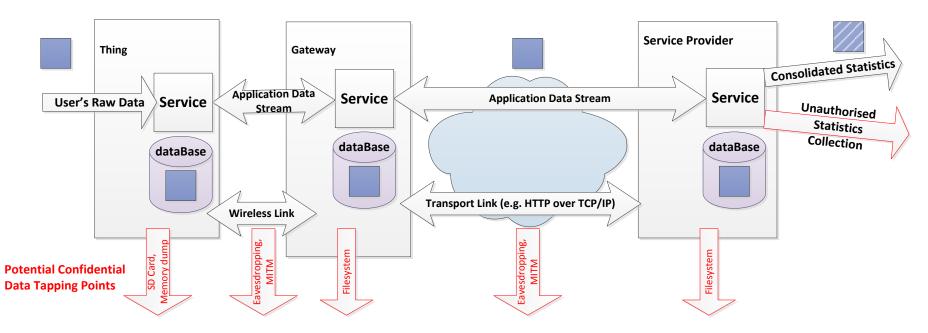

#### **IOT-The connected era of everything**

- Connection of things to internet

- Vulnerable to cyberattack

#### WHAT CAN WE EXPECT TO LOSE? IS IT WORTHWHILE TO HACK?

# Security motivations for IoT eco-system CSR

- Many opportunities for attacks!

- Securing Communication Channels just part of the solution.

- Security is hard and needs hardware support

The section looks at hardware authentication and encryption

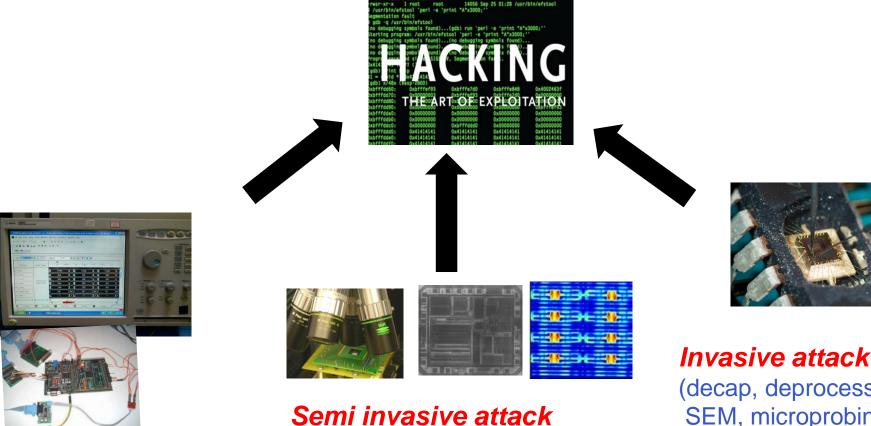

#### What The HACK?

Non invasive attack (glitch, clock, power attack)

(NIR imaging, Laser imaging, fault injection)

Invasive attack (decap, deprocessing, SEM, microprobing, FIB)

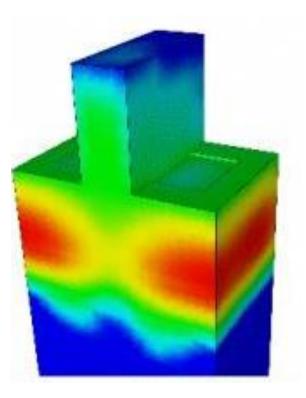

#### **Si Manufacturing Variations**

#### Random dopant fluctuation

#### Gate oxide thickness

Line edge roughness... Confidential © Cambridge Silicon Radio Limited 2015

- Nothing is deterministic anymore.

- Can we use this variation to create an unique DNA of every single chip?

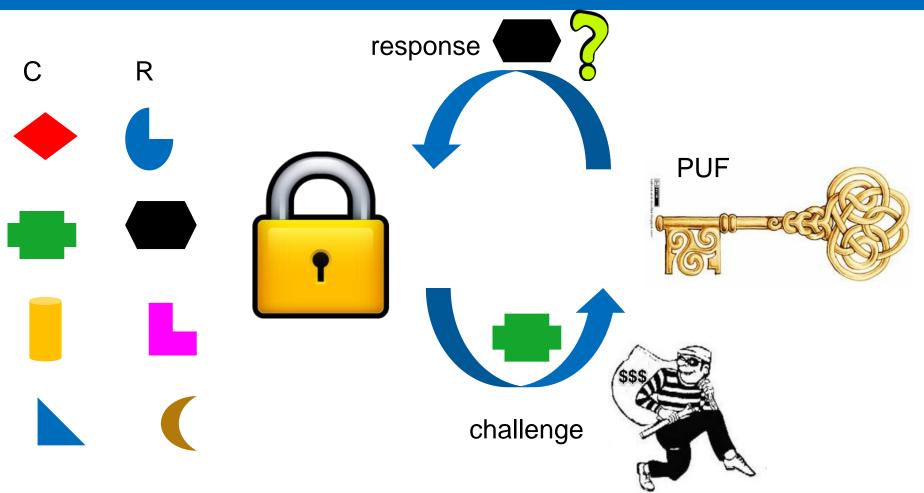

*Physically Unclonable Function* (*PUF*):

"A function whose execution depends on inaccessible and irreproducible variations caused by Silicon's manufacturing process. This serves as the generation of keys – basis of the whole root of trust and security aspects."

#### Silicon PUF and the Hardware Root of Trust Goal

Features - Tamper and Side Channel Attack resistant, Hard to Reverse Engineer, Reliable, and low Cost.

#### **Security is essential**

2/3/4 JUNI 2015 JAARBEURS UTF

|       | <ul> <li>Write once public<br/>unique id per chip<br/>at manufacturer</li> <li>ID accessible<br/>by FW/Apps<br/>layers</li> <li>This ID will<br/>associate to a<br/>unique key set</li> </ul> | <ul> <li>Unique pair of<br/>private/public key<br/>per chip (Root Key<br/>Set)</li> <li>Embedded in<br/>every single<br/>chip by<br/>manufacturer</li> </ul> | Root Identity<br>Module using RKS<br>to securely<br>sign/encrypt/decrypt<br>ID and config data | Root of Trust:<br>privileged FW<br>execution to sign<br>ROM/RAM fw and<br>apps and use RIM<br>to sign and safely<br>store signatures |                                        |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| ID io | dentifies chip's public k<br>Confidential © Cambridge Silicon R                                                                                                                               | To sig                                                                                                                                                       |                                                                                                | Root ID module used to<br>store FW signatures                                                                                        | o sign and<br>ECTRONICS<br>*AUTOMATION |

#### **Comparison of NVM vs PUF**

| Technology | Advantages                                                                                                                       | Disadvantages                                                                                                                             |

|------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| NVM        | <ul> <li>Erasable</li> <li>Testable</li> <li>Reliable</li> <li>Low overheads</li> </ul>                                          | <ul> <li>Easy to reverse<br/>engineer</li> <li>Require secure<br/>access path</li> <li>Need special process<br/>step-&gt; cost</li> </ul> |

| PUF        | <ul> <li>Difficult to reverse<br/>engineer</li> <li>Inherently generated<br/>key</li> <li>No special process<br/>step</li> </ul> | <ul><li>Not erasable</li><li>Not testable</li></ul>                                                                                       |

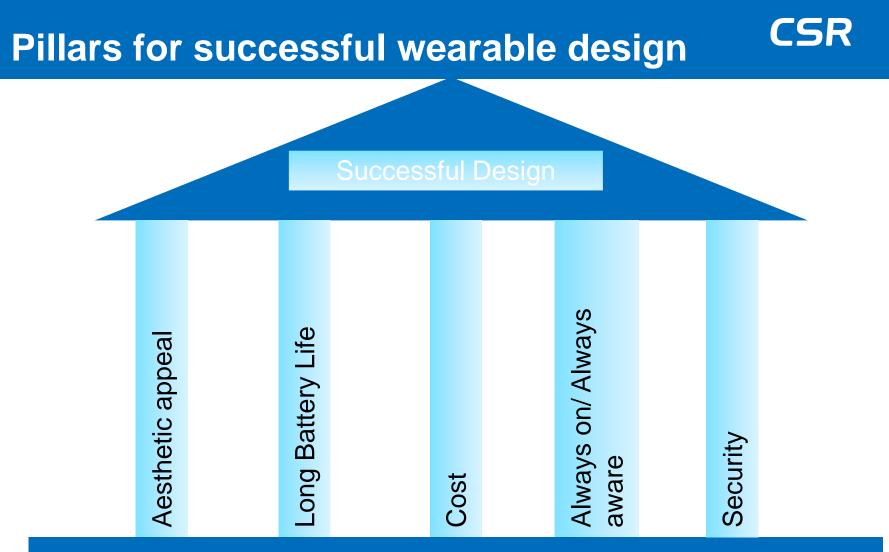

## <u>In Summary</u>

- Wearables are evolving and revolutionizing our engagement with ourselves and the world around us.

- We have identified the important factors

Aesthetics

Power Consumption

Cost

- Always On and Awareness

- Security

- These all present challenges to consider as we move forward.

# Push every boundary.®