# TOPIC EMBEDDED SYSTEMS

software development

to application design covers

up of expertise include: and

areas of expertise include: and

operating systems: Windows

platforms: PC, ARM Cortex AIRIN

platforming languages: C.C.

8 Tech

Hardware platform for

## **ULTRASOUND INSPECTION**

Herman Kuster, Topic Embedded Systems

More details on www.gaudisite.nl

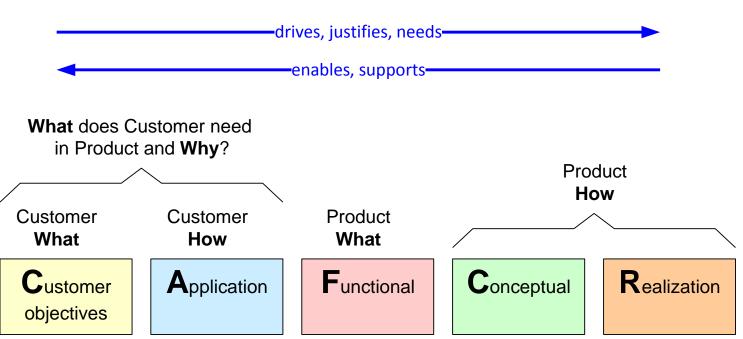

## Customer objectives

- Strong in Ultrasound inspection of steel

- Using third party hardware and software for years

- Wish to supply whole system including own hardware and software

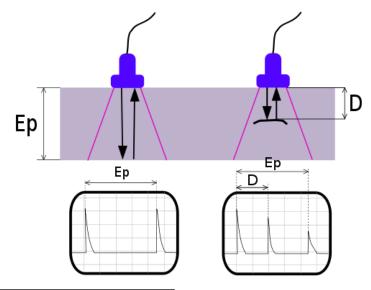

- Ultrasound inspection

- Detection of cracks and bubbles

- Sensor consists of piezo actuator and piezo sensor

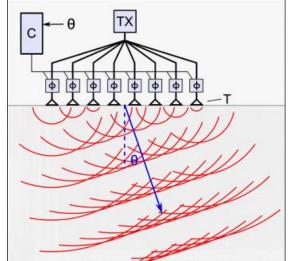

- Different types of sensors:

- Phased-array

- Multiple single-probes

# Application

## Functional (requirements)

#### Interfaces:

- Max 64 Probe connections

- Piezo UT, EMAT Probe connections

- External clock and trigger input/output

- 1G and 10G ethernet

- Several low-speed interfaces like:

- ▲ Encoders (RS-485)

- Fieldbus to machine control

- ▲ LVDS and HDMI display output

- ▲ SPI and I2C interfaces

## Processing platform:

- FPGA fabric for high-speed parallel processing

- ▲ CPU cores for feedback loops and management tasks

- Modular and scalable

- Industrial PC or Single board computer

- ▲ CPU-SOM, FPGA-SOM, Zynq-SOM

- Full custom built system

- Miami+, SOM with Xilinx Zynq

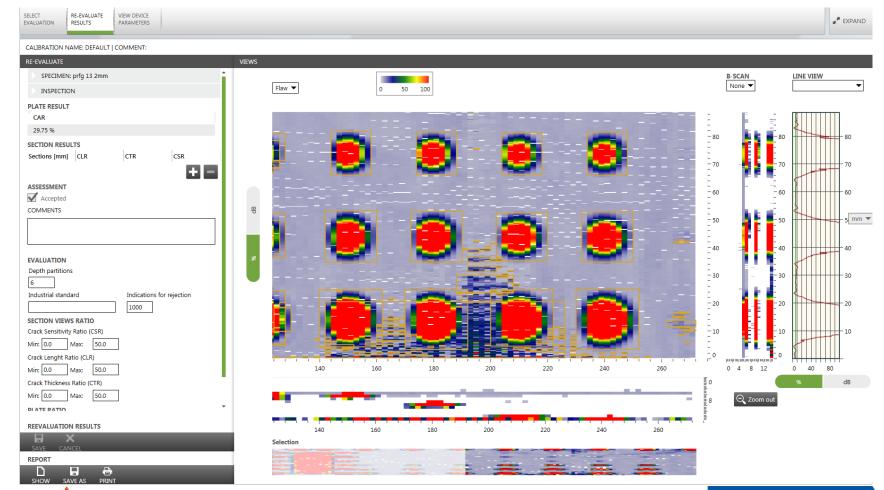

## Realization

- Miami+ SOM

- System overview

- Data processing

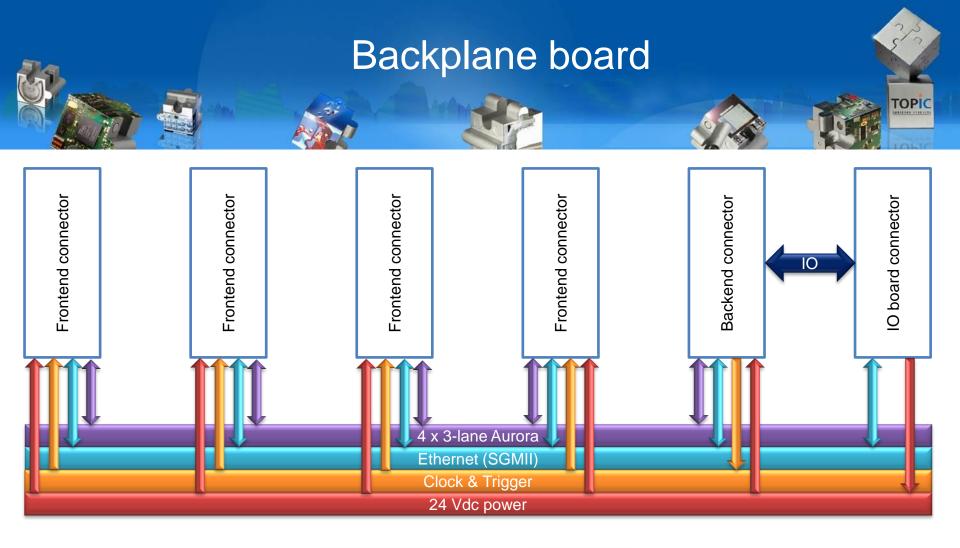

- Backplane board

- Frontend board

- Backend board

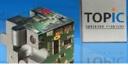

#### Miami+ Zynq-SOM TOPIC 1 GB DDR3 Clocks **Ethernet SDIO** Clocks **JTAG UART** Zynq-PS Clocks Flash 12C HP-IO Power 1GB DDR3 HP-IO HP-IO 200 pins HR-IO GTX HP & HR-IO GTX 16-lanes

HR-IO

HR-IO

Zynq-PL

On-board IO

GTX

GTX

HR IO

Zynq-SOM

**Embedded** in your future

**GTX**

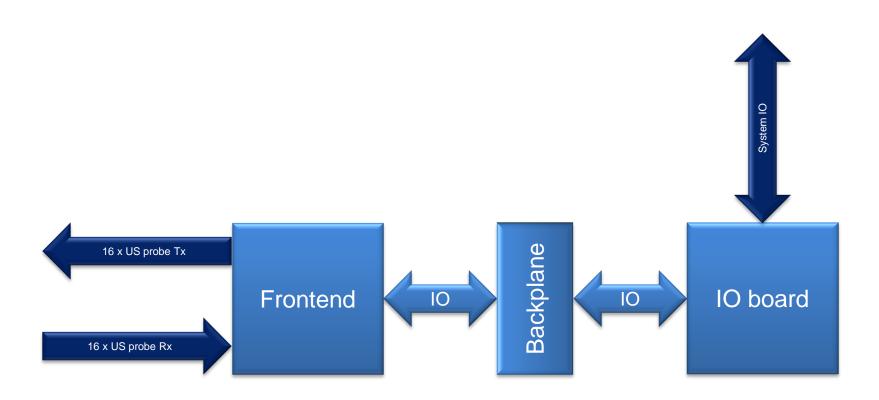

## Standalone system overview

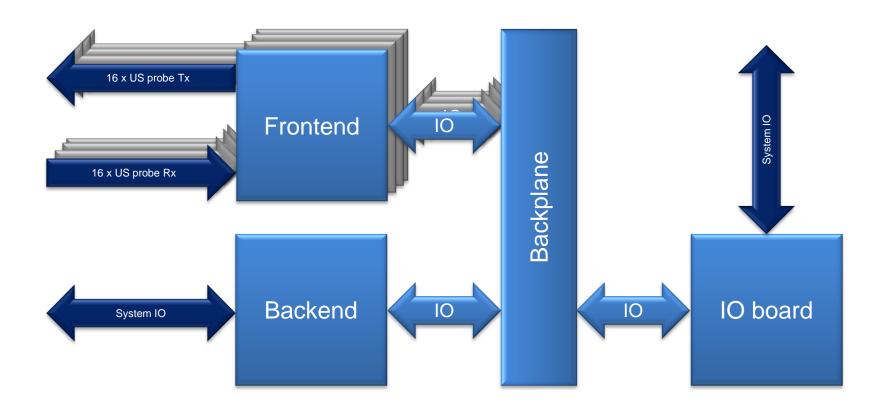

## Full system overview

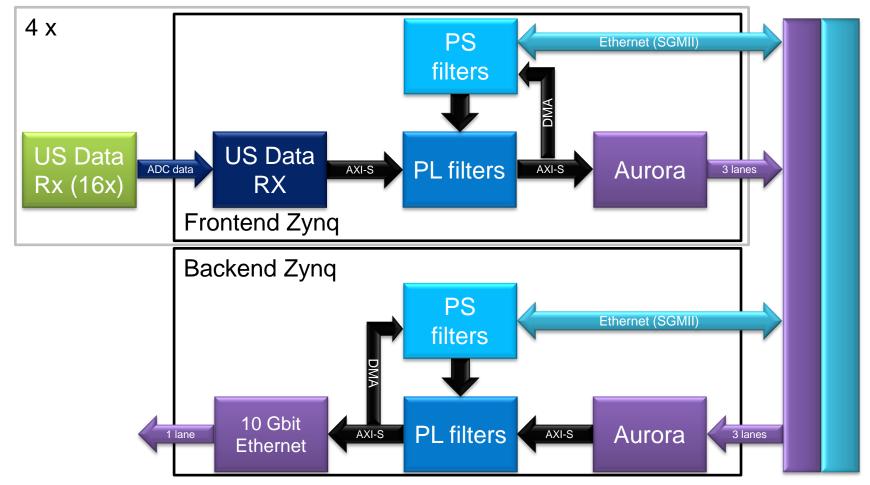

# Data processing for US Data

Gb Ethernet switch Clock & Trigger distribution

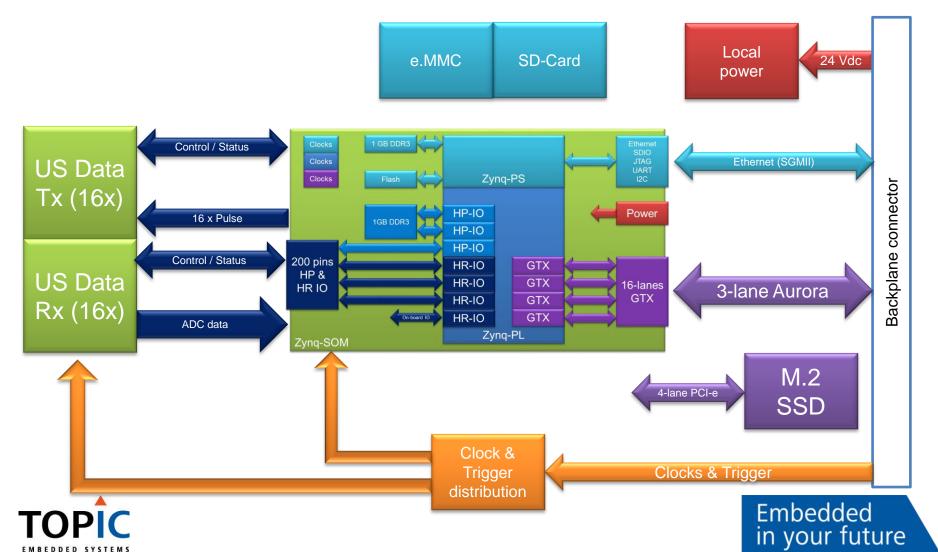

## Frontend board

### Backend board

HR IO

Zynq-SOM

Backplane connector

HR-IO

HR-IO

HR-IO

Zynq-PL

GTX

GTX

GTX

3-lane Aurora Clock &

16-lanes

GTX

Trigger distribution Clocks & Trigger

3-lane Aurora

3-lane Aurora

**Embedded** in your future

AnyBus

# Standalone system