CO-DEVELOPMENT MANUFACTURING INNOVATION & SUPPORT

# High-Level and Model-Based Design Targeting FPGAs and SoCs

Sander Ter Burg, FPGA System Engineer

#### **3T B.V.**

- What we do:

- Electronic and Embedded Systems

- Co-Development and Re-design

- Manufacturing (together with production partners)

- Consulting & Support

- Where we are:

- Enschede + Eindhoven

- More info:

- www.3T.nl

- info@3T.nl

#### **Summary**

- High-Level Design and Synthesis

- Model-Based Design

- Model-Based Design Examples

- SCARA Robot Braking Controller

- Radar Tracking Module

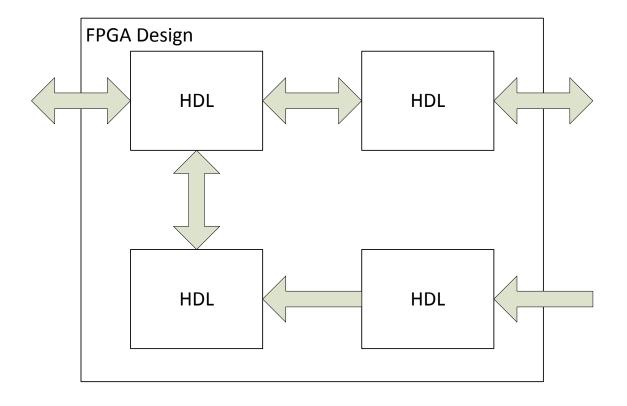

# Traditional HDL Design example

- All code written in HDL

- No CPUs on-board

- HDL to Low Level Logic

HDL = Hardware Description Language

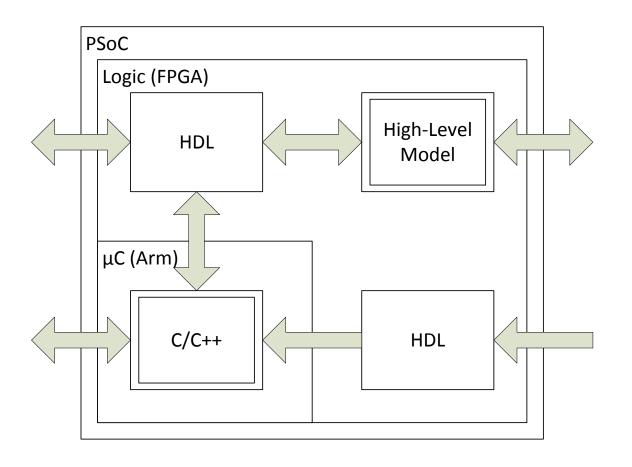

# High(er)-Level Design example

#### Higher Level Design Blocks

- High-Level Model to HDL

- C/C++ code running on a CPU

#### HLS examples

- C/C++ to HDL + synthesis

- MATLAB to HDL + synthesis

- ... to HDL + synthesis

# **High Level Design Tools**

#### For FPGA devices:

- Vivado HLS (Xilinx)

- HLS Compiler (Intel)

- HDL Coder (MathWorks)

- and more...

#### For SoC devices:

- SDSoC (Xilinx)

- SDK for OpenCL (Intel)

- Embedded Coder (MathWorks)

- and more...

# High Level Design Pros ...

- Well suited for complex mathematical problems

- Fast Functional Iterations

- Freedom of implementation (CPU and/or Logic)

- Simulation time reduction (in software)

- Early resource estimation

- HDL Co-Simulation in software environment

# High Level Design Cons ...

- Hardware mind-set still needed

- Code restructuring needed

- Generated HDL is not very readable

- Less suitable for (peripheral) interface controllers

- But... tools keep getting better

#### **Model-Based Design**

- A form of High-Level Designing

- Mathematical and visual design method

- To design:

- Complex controllers

- Signal processing

- Communication systems

- Applications fields examples:

- Industrial

- Aerospace

- Automotive

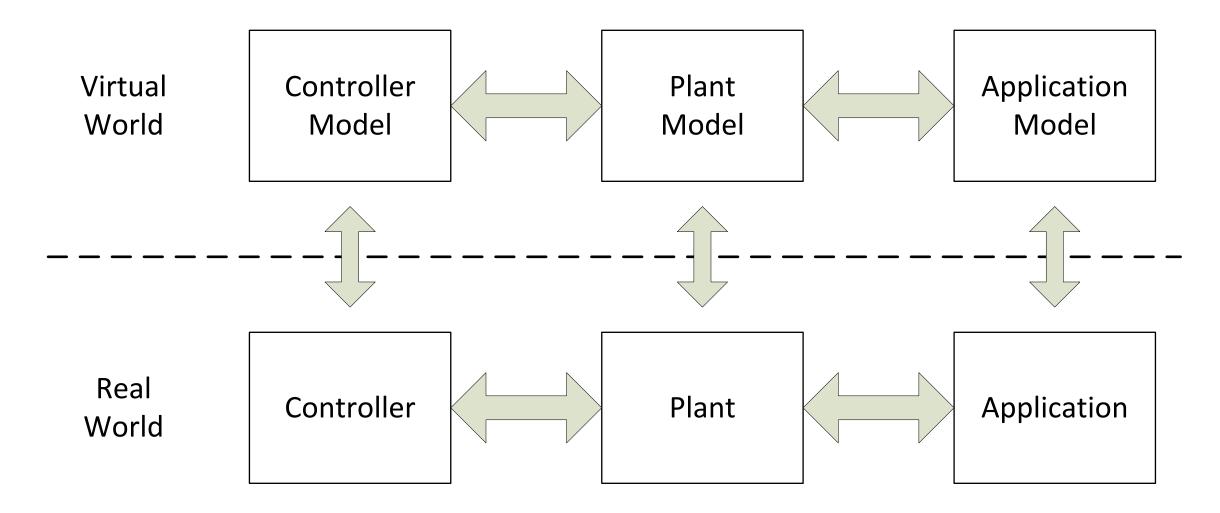

#### Real vs. Virtual World

#### **Model-Based Design**

- Multidisciplinary Design Approach

- Design with Virtual Models (without hardware)

- Simulation in the Virtual environment

- Models are always a complexity / effort trade-off

- Controller Model as good as your Plant/Appl. Model

# Model-Based Design Examples

- SCARA Robot Braking Controller

- Radar Tracking Module

# **SCARA Robot Braking Application**

- Move intermediate semiconductor products

- Controlled emergency braking

- Braking Requirements:

- Follow robot trajectory while braking

- Deviation from trajectory < 1mm</p>

- Rest is under NDA... 🧽

- Customer provided Mechanical Models (in MATLAB Simulink)

- SCARA Motor Model

- Controller Model

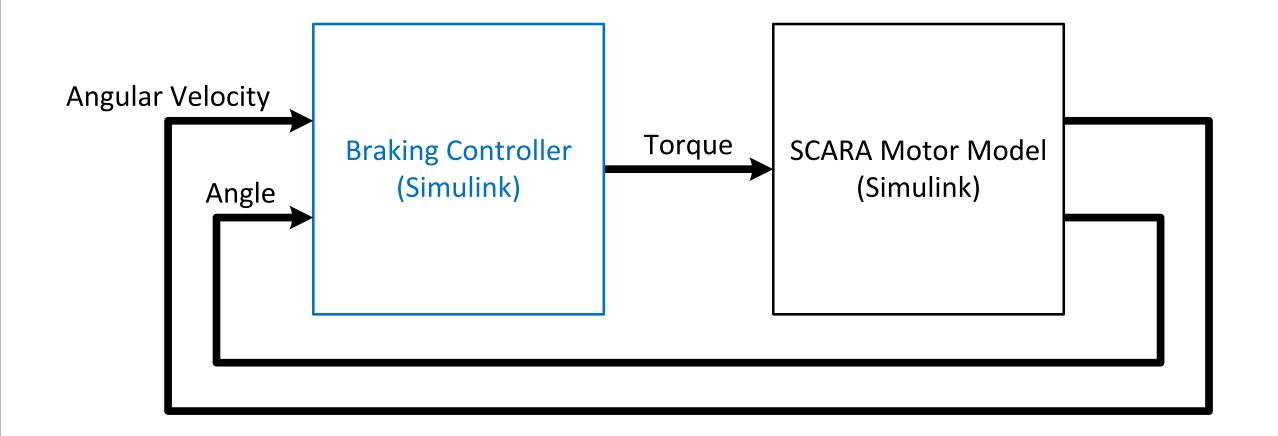

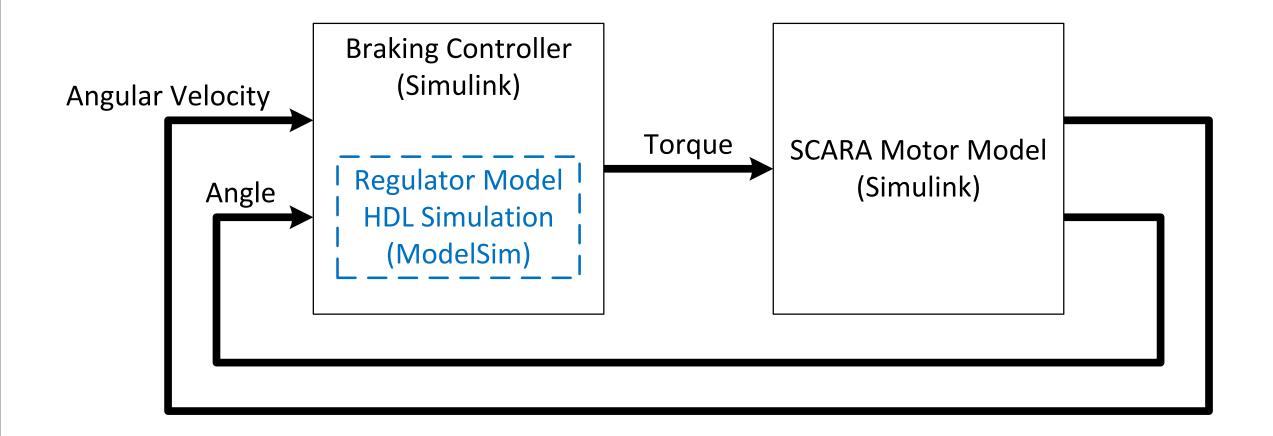

#### Simulink Model of Plant and Controller

# Simulink Braking Controller Model

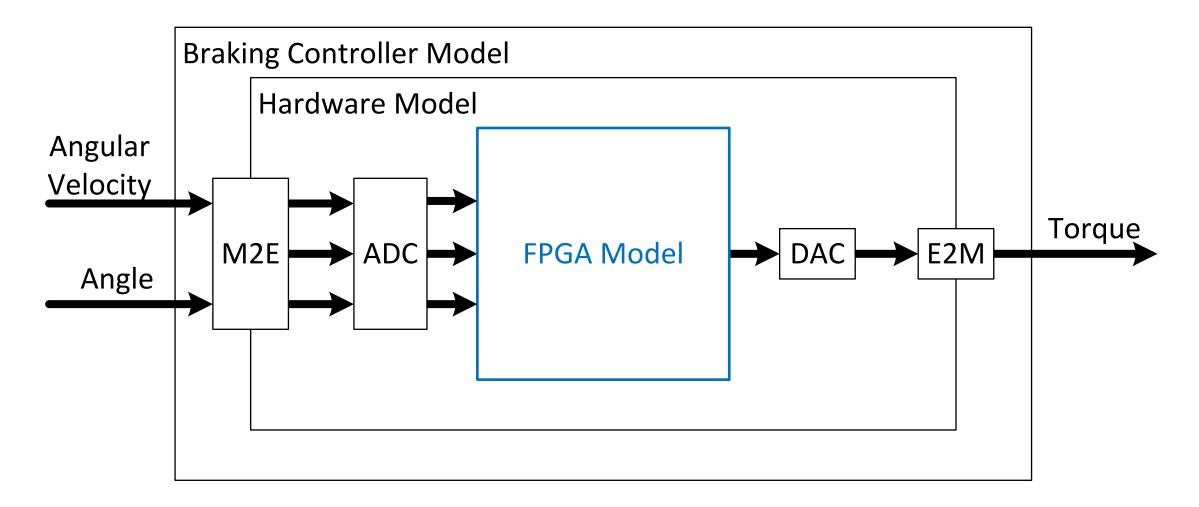

#### Simulink FPGA Model

www.3t.eu

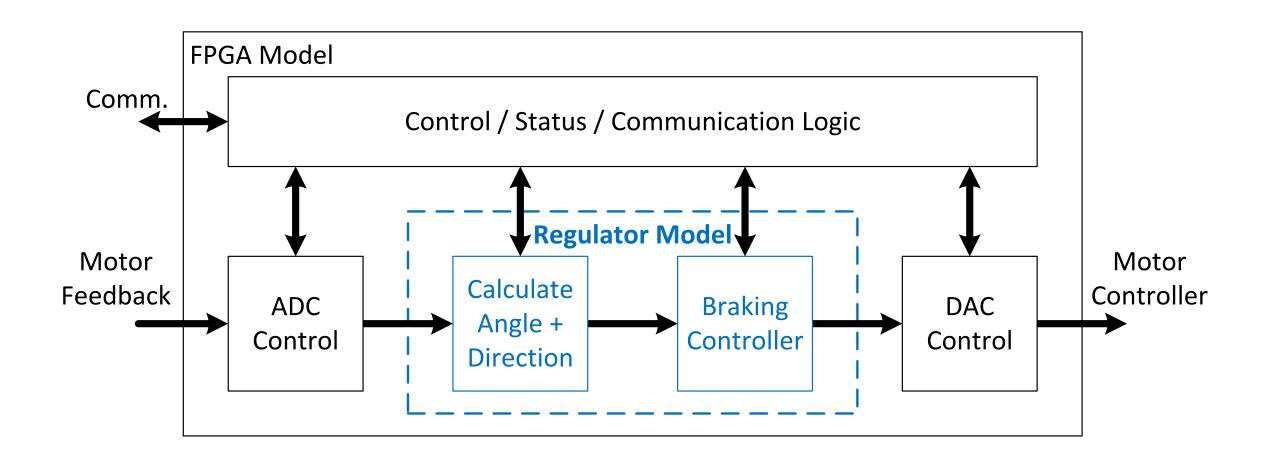

# Simulink Braking Regulator (Model to HDL)

#### **Braking Regulator HDL Co-Simulation**

#### **Design and Verification Summary**

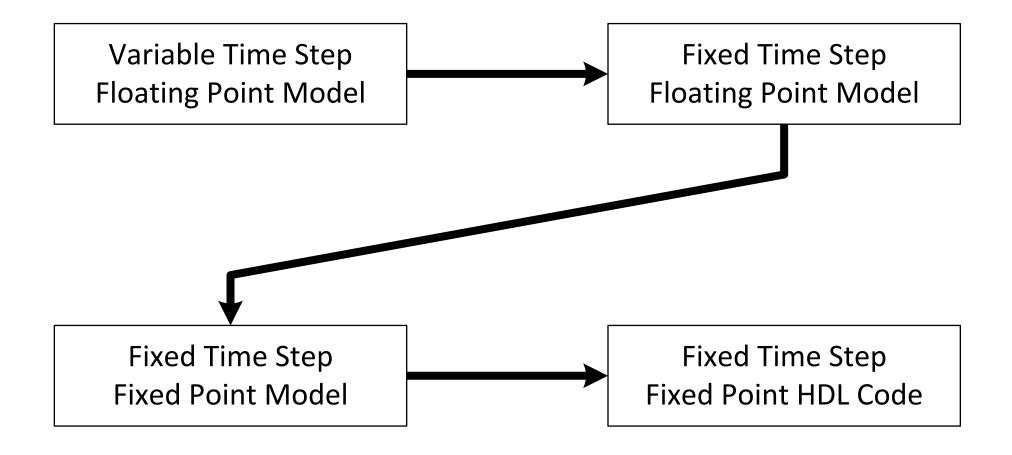

- From "High Level Model" to "Generated HDL"

- Various Model Translations

- Generated HDL for Regulator Model (HDL Coder)

- Angle/Direction Calculation + Braking Controller

- Hardcoded Design Blocks (non HDL Coder)

- ADC / DAC Control + Control / Status / Communication Blocks

- Design Verification:

- Co-Simulation + Hardware-in-the-Loop

- Design Fine-tuning:

- Timing Closure, Resource Sharing,

- Xilinx IP Instantiation for FFT

# Radar Tracking Module example

- For Traffic Data processing

- Customer provided a High-Level Model (MATLAB) including:

- Radar Module

- Signal Processing

- Tracking Algorithm

- System-on-Module Hardware Target

- Enclustra Mars ZX3

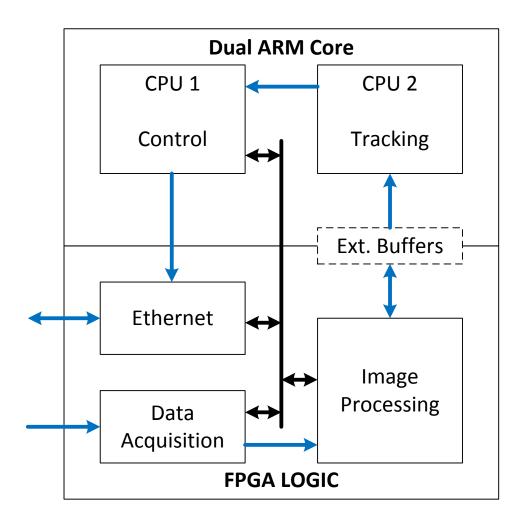

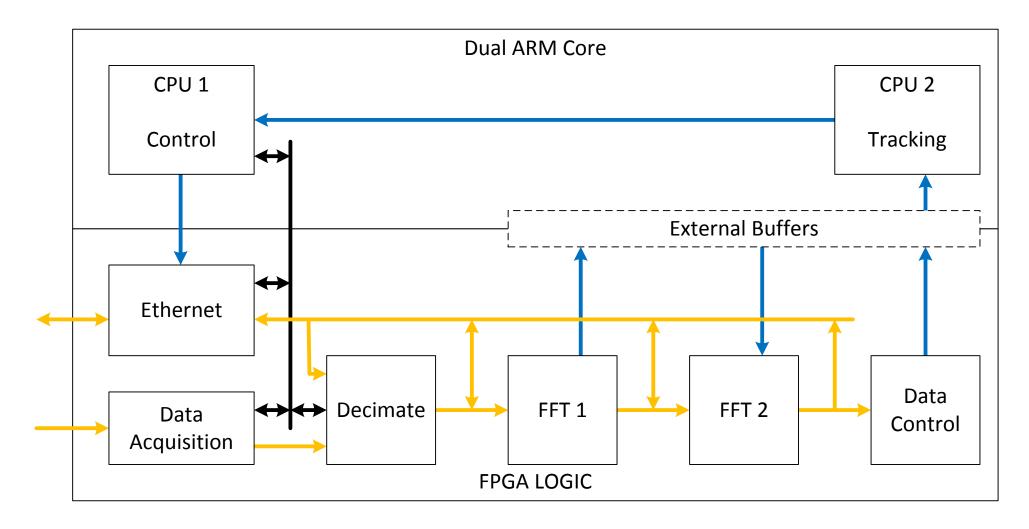

# SoC implementation setup

- eCos RTOS on CPU1

- For real-time Control and Communication

- Only available RTOS for this SoM

- Tracking Algorithms on CPU2

- Generated C/C++ from Matlab Model

- Running bare-metal on CPU2

- Image Processing in FPGA LOGIC

- 2D Traffic Data Matrices Operations

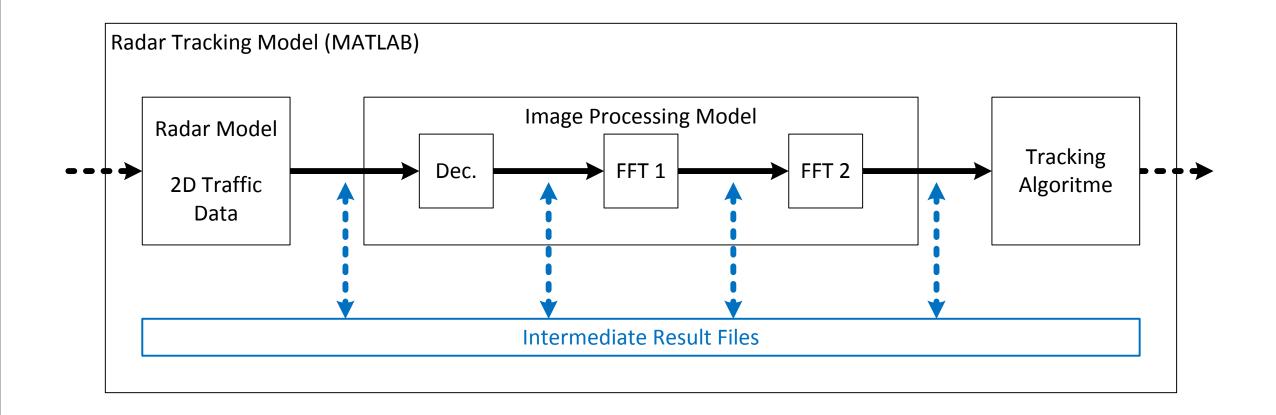

# Radar Tracking Model

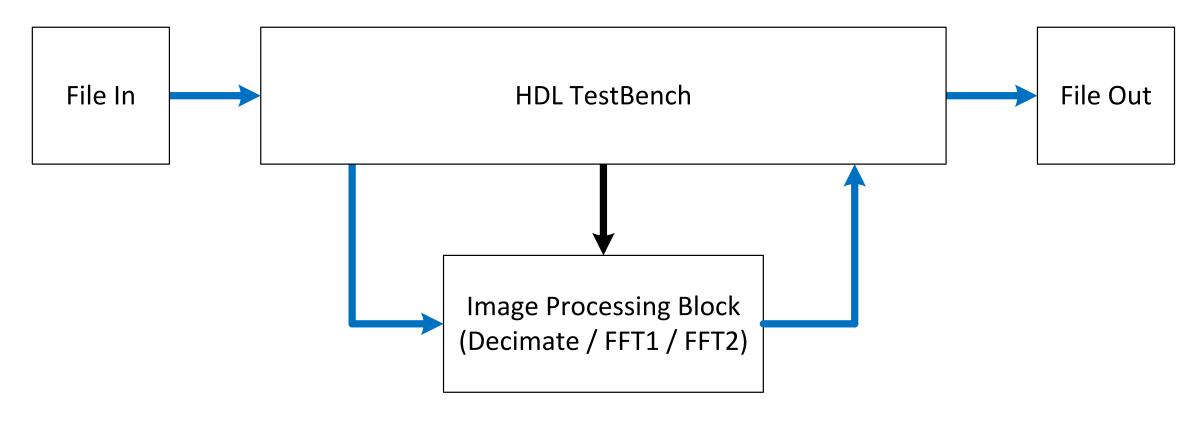

#### **Image Processing Module Simulation**

- Intermediate Model Results used in HDL TestBench

- HDL TestBench Results verified in the Model

# Hardware-in-the-Loop Verification

# **Tooling**

- Mathworks Tools:

- MATLAB: Complete Radar Tracking Model

- Embedded coder: *Tracking Algorithms Implementation*

- Instrument Control toolbox: Hardware-in-the-Loop Verification

- Signal processing toolbox: Digital Filter Design

- Xilinx Vivado:

- Xilinx IP: FFTs for Image Processing

- Xilinx IP: Gbit Ethernet for UDP communication

- Custom IP: Decimate for Image Processing

- Xilinx to MATLAB: Xilinx FFT C-model converted to MATLAB file

#### **Summary and More Info:**

- High-Level Design and Synthesis

- Model-Based Design

- SCARA Robot Braking Controller

- Radar Tracking Module

■ Email: Sander@3T.nl

■ Web: www.3T.nl

■ Stand: 7A108

#### Next Up:

- Herman Kuster

- Topic Embedded Systems

- Hardware platform for industrial ultrasound steel plate Inspection

#### electronics & embedded systems

#### **3T B.V.**

Institutenweg 1 7521 PH Enschede

Esp 401 5633 AJ Eindhoven The Netherlands The Netherlands

T. +31 53 4 33 66 33

F. +31 53 4 33 68 69

E. info@3t.nl

W. www.3t.eu