## Snel en veilig hardware testen

**Logic Technology**

#### **SOLUTIONS**

Software Quality

Software Components

Logic Technology offers a variety of tested software components that make sure your design meets the industry standards and assure compatibility now and in the future.

#### **SOLUTIONS**

**Boards & Solutions**

Logic replaces the complexity of the hardware design and helps to improve overall board testability by offering a wide range of standard and custom made modules and supplies.

Logic Technology keeps you agile with high performance, feature rich, development tools and debuggers, tuned for various microcontroller and processor architectures.

## **TEST**

- What?

- Why?

- at any Cost ?

- How ?

- Challenge?

- Solution ?

## **What Test**

- Smoke Test

- PCB Inspection

- ICT / FP

- Prototype Test/Debug

- JTAG

- Functional Testing

#### What Test?

From Wikipedia, the free encyclopedia

Automatic or automated test equipment (ATE) is any apparatus that performs tests on a device, known as the <u>Device Under Test</u> (DUT), Equipment Under Test (EUT) or Unit Under Test (UUT), using <u>automation</u> to quickly perform measurements and evaluate the test results.

## **TEST**

- What?

- Why?

- at any Cost ?

- How ?

- Challenge ?

- Solution ?

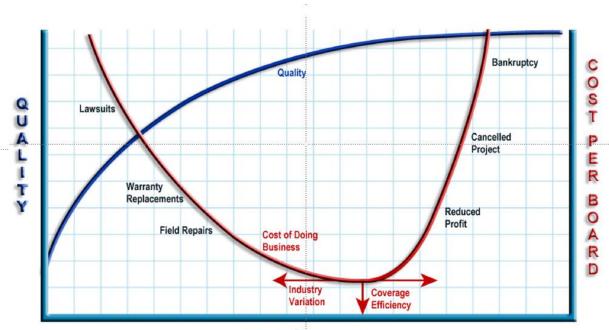

## Why Test?

- Customers

- Short Term vss. Long Term Costs

If you don't have time to do it right, when will you have time to

do it over?

( John Wooden )

## **Skip Functional Test?**

- Seems a silly question but considerable companies still only box test or only conduct basic tests on raw electronic assemblies.

- > Basic tests can be just visual inspection

- Test equipment is often deemed too expensive and requires to much resources to implement.

- Especially if the volume is low

- Labour cost are increasing

## **Skip Functional Test?**

- Most 'Test' Engineers in smaller / medium size organisations do not have the required skills to develop complex test equipment.

- Companies cannot afford to employ full blown electronic engineers

- > As hardware get more complex so does the testing requirements

- Obviously the answer is 'NO' but the pressure on reducing budgets normally means that 'Functional Testing' is given a significantly lower priority

## **TEST**

- What?

- Why?

- at any Cost ?

- How ?

- Challenge?

- Solution?

## **Test at any Cost?**

- The metric of development and test efficiency is typically a formula that includes the following factors:

- 1. Cost

- 2. Duration

- 3. Safety

- 4. Feasibility

## At Any Cost?

**Test Coverage**

## **TEST**

- What?

- Why?

- at any Cost ?

- How ?

- Challenge ?

- Solution ?

Write a Testplan

> IMPOSSIBLE only means you haven't found the Solution yet

A test plan documents the **strategy** that will be used to verify and ensure that a product or system meets its design specifications and other requirements.

A test plan is usually prepared by or with significant input from Test Engineers

#### Methods

- test methods may be determined by standards, regulatory agencies, or contractual agreement

- test equipment to be used in the performance of the tests and establish pass/fail criteria

#### Responsibilities

- test methods at each stage of the product life

- plan, acquire or develop test equipment and other resources necessary to implement the test methods

One outcome of a successful test plan should be a record or report of the verification of all design specifications and requirements as agreed upon by all parties

## **DFT**

> add certain testability features to a hardware product design

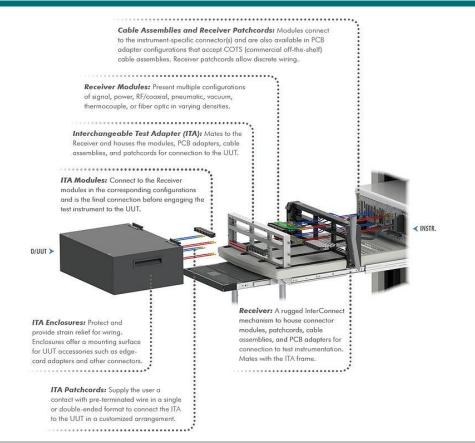

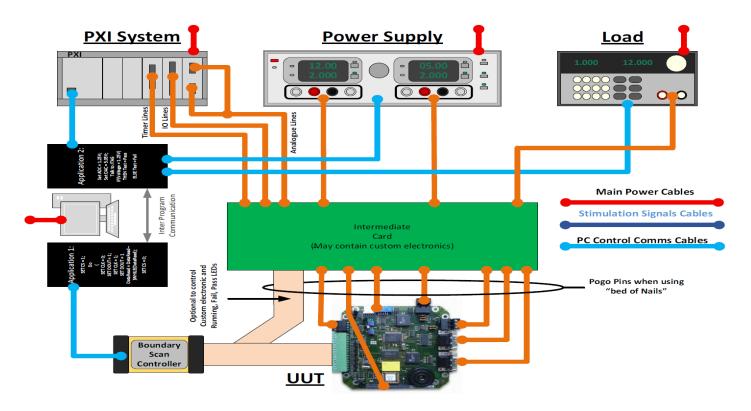

## **How To Connect?**

From Wikipedia, the free encyclopedia

**Mass interconnect** systems act as the connector interface between test instruments (<u>PXI</u>, <u>VXI</u>, <u>LXI</u>, GPIB, SCXI, & PCI) and devices/units under test (D/UUT).

Used in <u>defense</u>, <u>aerospace</u>, automotive, <u>manufacturing</u>, and other applications. By mating a receiver on the tester side with an **interchangeable test adapter** (ITA) on the UUT, the mass interconnect enables the entire system to mate together at one time. Mass InterConnect systems are available in multiple sizes and configurations to accommodate virtually any testing requirement.

#### **Pro's and cons of ATE / Testracks**

#### Good

- Small

- Modular

- Wide variety of modules

- Rapid Test development

- Reduce Overall Cost

#### Reality

- Big

- Expensive Capital invest

- Require adaptation (Fixtures

) for each UUT.

- Costs on HW and SW Program development.

#### **TEST**

What Test?

Why Test?

Test at any Cost?

How to Test?

**Challenge?**

Solution?

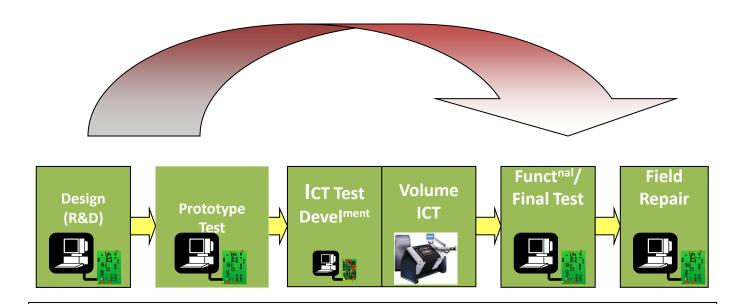

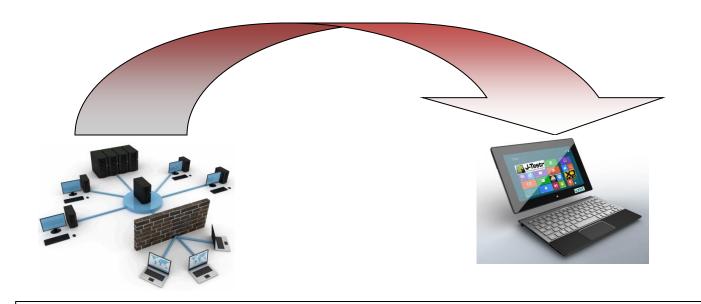

## Challenge

Create a highly integrated Test concept in terms of being portable throughout the lifecycle

## Challenge

Remove software Overhead to simplify the development and reduce deployment costs

#### **TEST**

What Test?

Why Test?

Test at any Cost?

How to Test?

Challenge?

**Solution?**

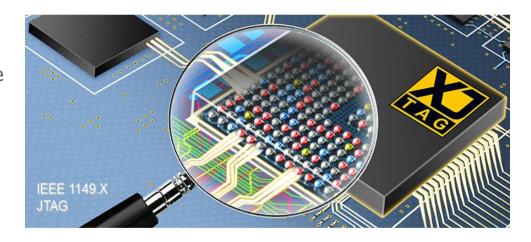

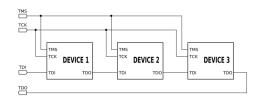

## JTAG compatible Functional Tester

#### **JTAG**

#### Boundary Scan IEEE 1149.1

- Std= interface description

- vendor lock you in

- SW development requires expertise

- Digital only

Test Extensions ( I/O modules )

- Manufacturing Test

- Program Devices

- Still Requires FUNCTIONAL TEST

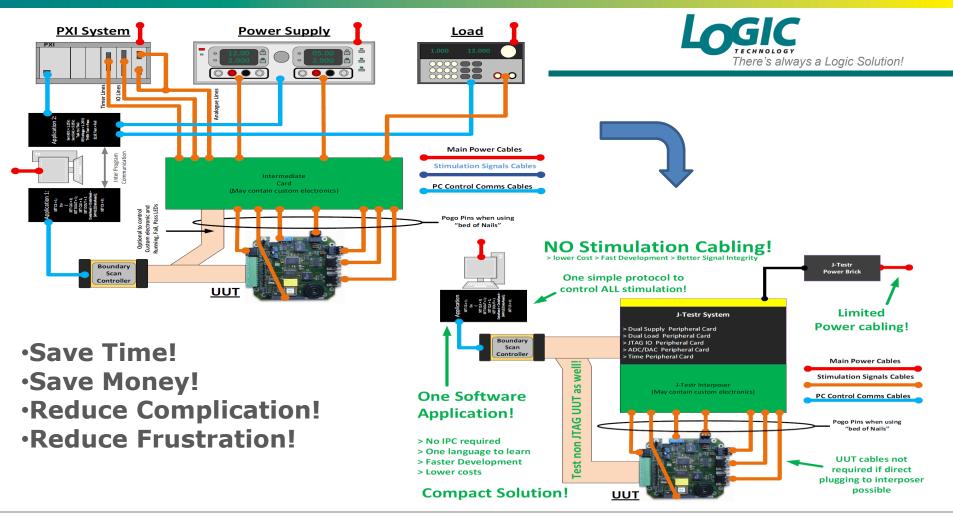

## **Block Diagram**

## **Solution**

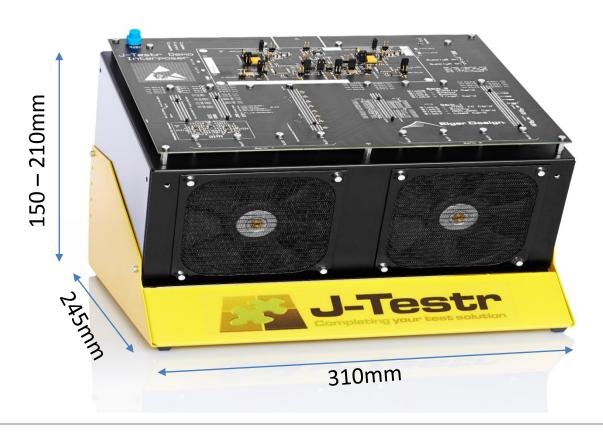

# J-Testr By Eiger Design

## Solution

- Very compact mechanical solution

- Easily reconfigurable/customisable

Simple to remove interposer (personality card)

- Simple and cheap Interconnection between test elements and UUT

- Limited and in some cases NO cabling required

- Quick and Easy Interchangeable test elements (peripherals cards)

- Easily expandable

- Easy to design special custom test elements (peripherals cards)

- Open hardware peripheral front end with development board

- Integrated flexible power system

- Integrated cooling and advanced UUT power safety considerations

- Protects untested UUT and equipment from power faults (rail shorts, OV conditions)

- Maintains test environment

- Single simple test software

- One language to learn

- Faster Development

- Lower costs

- NO IPC required

- Provide a common test environment Even for non JTAG UUTs!!!!

- Maximise the JTAG Boundary tool investment

- Common test platform

- Fast and simple memory mapped interface

Compared to IO bit bashing communications (SPI, I2C, etc) over JTAG

- Instantly familiar to any engineer with Microprocessor/Microcontroller experience

## **UUT Mounting Options**

- Direct Mounting to Interposer

- > If UUT connections and size allows

- Cheapest/fastest option

- UUT mounted to the UUT attachment plate

- Connected via short cables from interposer

- > UUT mounting plate is a very simple four sided sheet metal design

- Easy and cheaply customisable for the UUT

- > Simple UUT mounting can be done drilling standard blank UUT attachment plate

- Low Cost

- Attachment plate height (distance from interposer card)

- Bed of Nails (J-Testr Integrated to 'Bed of Nails' rig)

- Higher volume testing

- Easy of user connection

# J-Testr Making Development Easier

#### **Breakout Cards**

- Every peripheral card comes with a breakout card to allow the user to get up and running immediately without a Interposer.

- Access to all the cards features

- Easily fitted in minutes

- > Speeds learning and development times

## **Remove Software Overhead**

- Marvin "ATEasy"

- Native Python

- Native C++ < requires Ethernet option> (in development)

- All Driver are open Source!!!!!

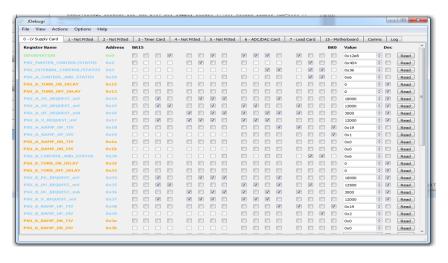

## **Improve Diagnostics**

- Software let you see inside each peripheral card

- > See what has been Read and Written

- > Read and Write registers directly

- Activity Log

- See the sequential activity

- Debug like a microcontroller!

## **Key Benefits**

- Complete 'All-in-One' Test solution.

- Control via JTAG or Ethernet interfaces, with native JTAG controllable IO peripherals available.

- Super flexible, customizable, 'Bed of Nails' compatible.

- Fully **integrated** system power and thermal management.

- Advanced power up safety features (protects UUT).

- Very easy reconfiguration, within minutes (for re-use on multiple projects).

- One software environment to control both the 'UUT' and the 'Test Stimulus' when using a JTAG environment.

- Easy-to-use and **fast** programming .

- Software language independent (works with all common test software systems.

- Simple/Low-cost personalization card ('Interposer') easily and quickly designed.

- Custom stimulation peripherals possible with 'open hardware' interface circuitry.

- Highly compact, portable, and easy to store solution.

Whether you think you can, or you think you can't - you're right.

(Henry Ford)