# Designing a Multi-Processor based system with FPGAs

Frank de Bont

Trainer / Consultant

Cereslaan 10b

5384 VT Heesch

① +31 (0)412 660088

☑ info@core-vision.nl

www.core-vision.nl

#### Why Use Processors?

- Microcontrollers (μC) and microprocessors (μP) provide a higher level of design abstraction

- Most µC functions can be implemented using VHDL or Verilog

- Downsides are parallelism & complexity

- Using C/C++ abstraction & serial execution make certain functions much easier to implement in a μC

- Discrete µCs are inexpensive and widely used

- µCs have years of momentum and software designers have vast experience using them

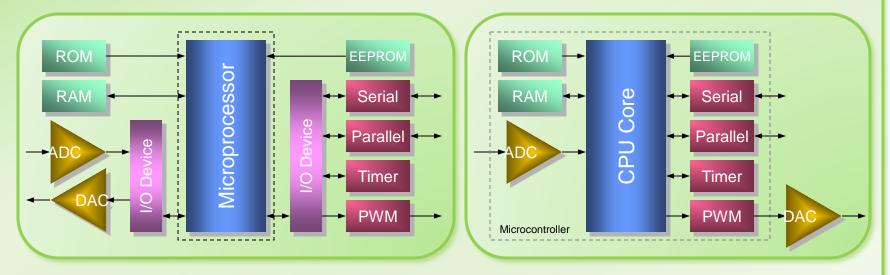

### μP versus μC

A microprocessor (µP) is just one component of many in a <u>complex system</u> of digital & analog I/O

Most <u>simple system</u> components are contained completely within a microcontroller (µC)

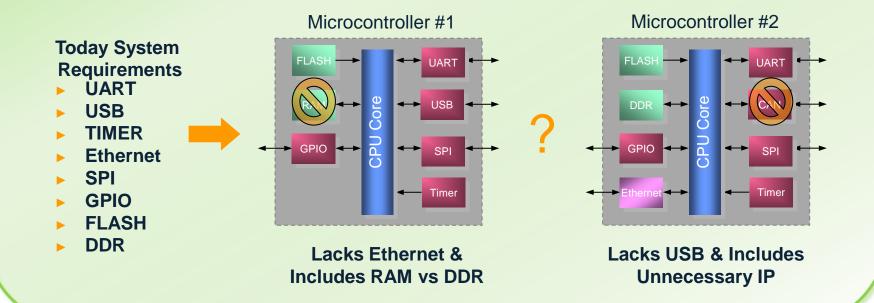

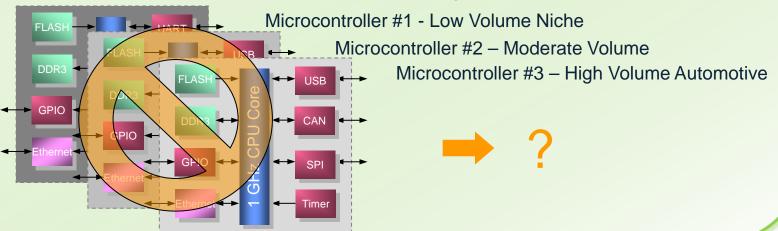

#### Rarely the Ideal Mix

Difficult to find the required mix of peripherals in Off the Shelf (OTS) microcontroller solutions

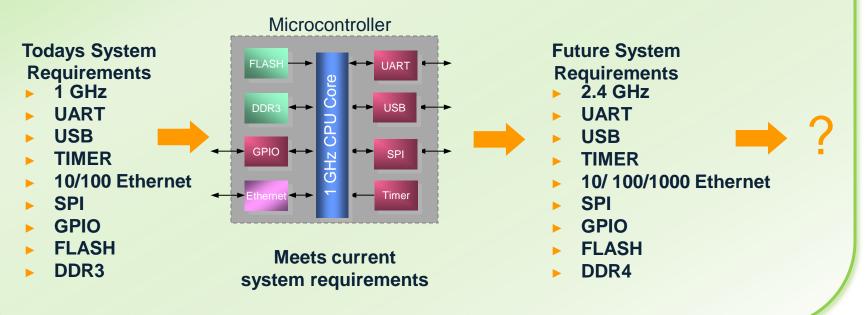

#### **Changing Requirements**

- Difficult to find the required mix of peripherals in Off the Shelf (OTS) microcontroller solutions

- Selecting a single processor core with long term solution viability is difficult at best

#### Here Today, Gone Tomorrow

- Difficult to find the required mix of peripherals in Off the Shelf (OTS) microcontroller solutions

- Selecting a single processor core with long term solution viability is difficult at best

- Without direct ownership of the processing solution, obsolescence is always a concern

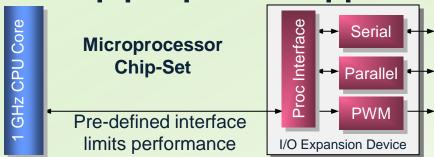

#### **Chipset Solutions**

- Difficult to find the required mix of peripherals in Off the Shelf (OTS) microcontroller solutions

- Selecting a single processor core with long term solution viability is difficult at best

- Without direct ownership of the processing solution, obsolescence is always a concern

- Many microprocessor based solutions provide limited On-Chip peripheral support

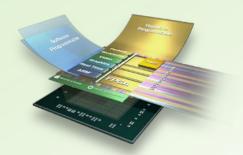

### **Embedded Design with FPGAs**

- FPGA allow for the implementation of an ideal mix of peripherals and system infrastructure

- New system requirements can be supported without changing the processor core

- Longevity of FPGAs approaches the longest available microcontrollers in the market

- FPGAs are used to augment μP functionality absorbing the core is the next natural step

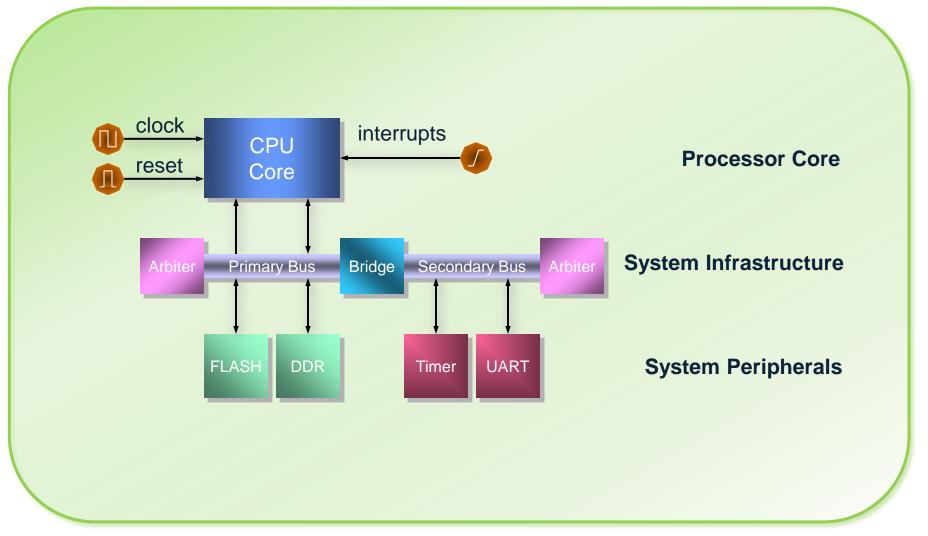

#### Simple Processor System

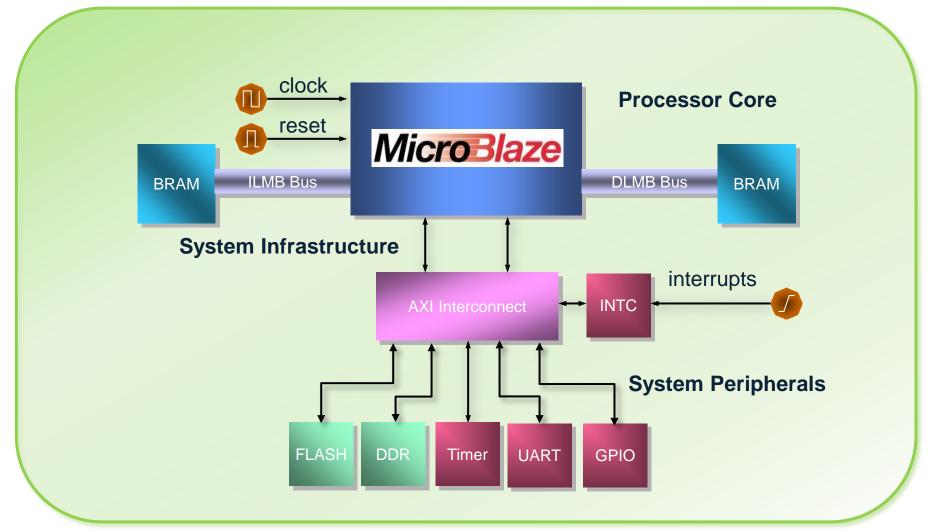

#### Softcore Processor System

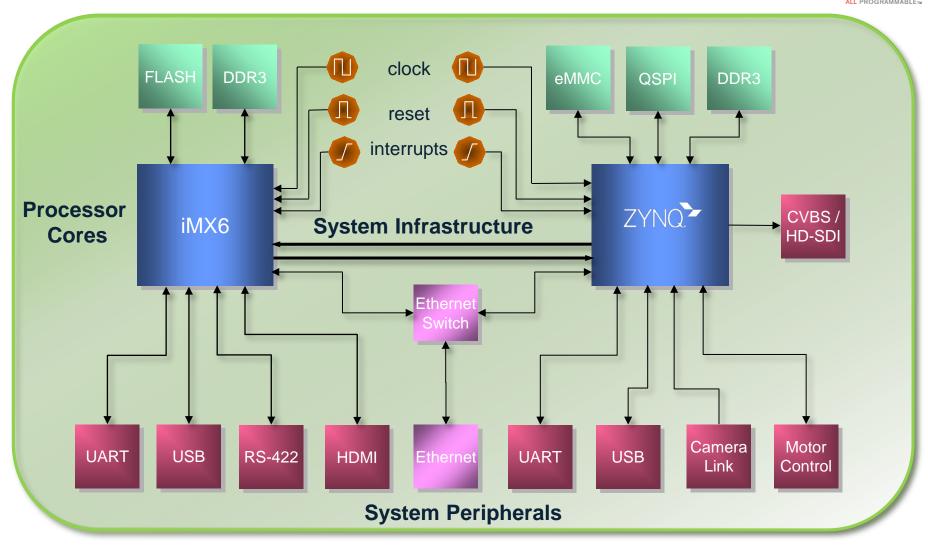

#### **Hybrid Processor System**

#### **Hybrid Processor System**

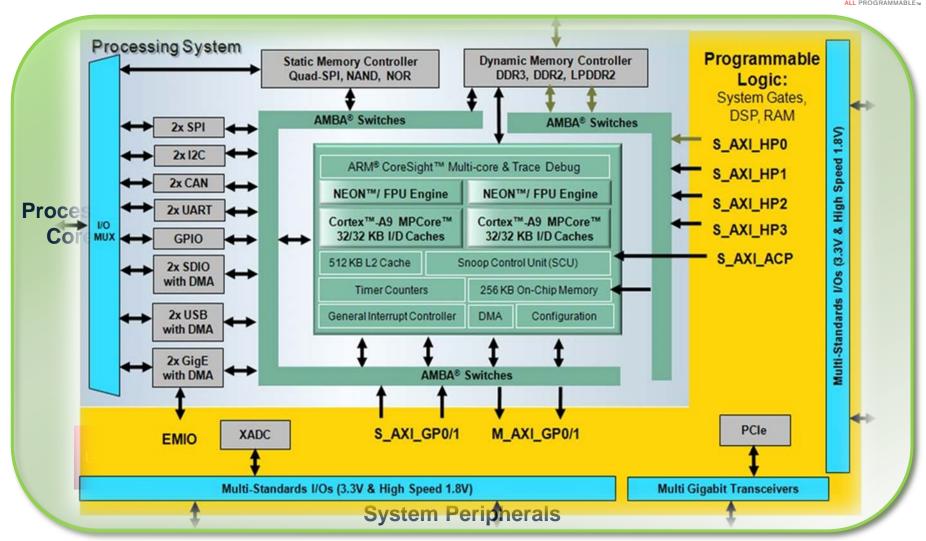

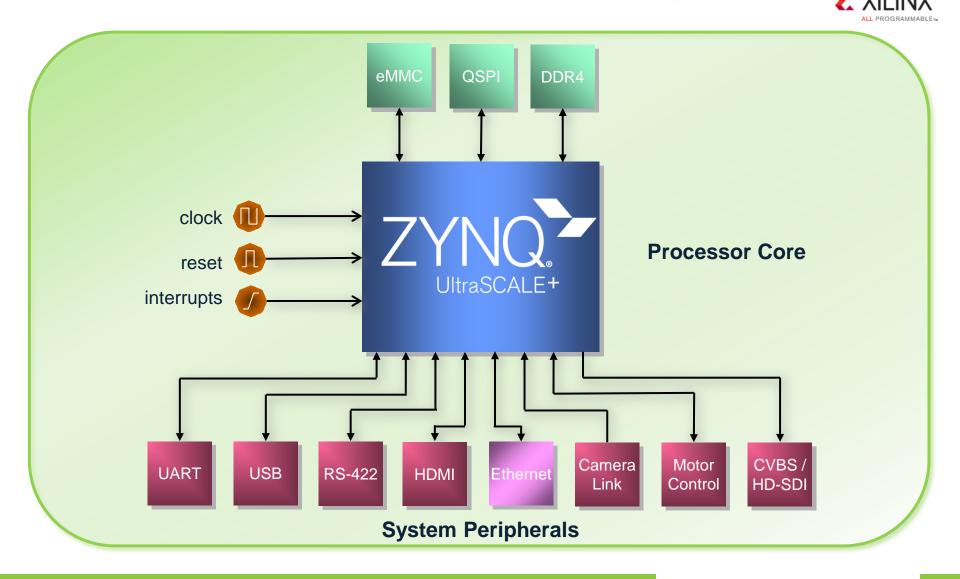

#### FPGA based Processor System

#### FPGA based Processor System

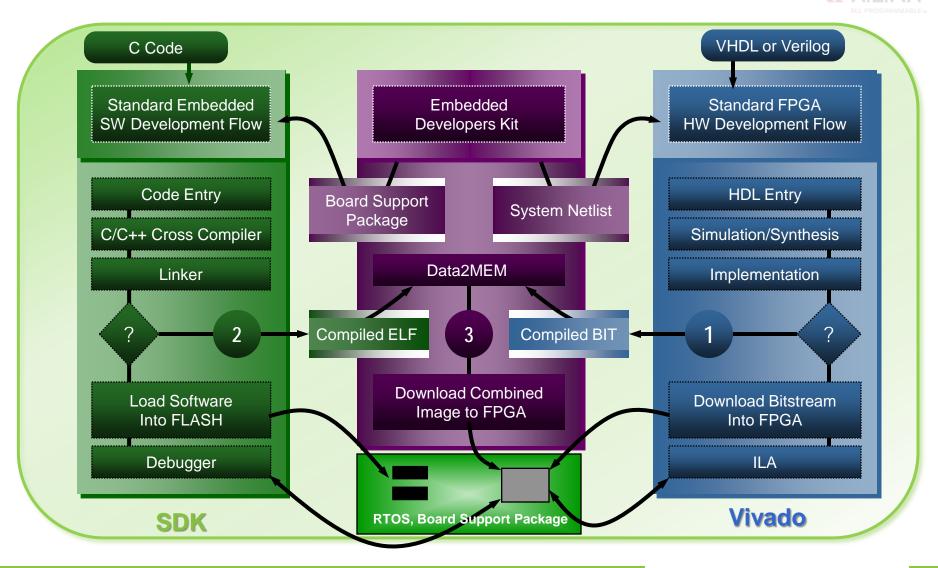

#### **Necessary Tools**

- A full complement of tools are required to design an embedded processor system

- Processor system generation

- Hardware implementation tools

- Software compilers

- Hardware debugger tools

- Software debugging tools

## **Necessary Tools**

- A full complement of tools are required to design an embedded processor system

- Processor system generation

- Hardware implementation tools

- Software compilers

- Hardware debugger tools

- Software debugging tools

- HW implementation & SW compilation are the two main flows that must be addressed

- The embedded flows should mirror traditional flows

### Traditional Embedded Design Flow

#### **Design Flow and Tools**

#### Software

- Real-time OS

- Drivers

- ► APIs

- **...**

#### ▶ Tools

- Vivado SDK

- Matlab

- ► SDSoC

**...**

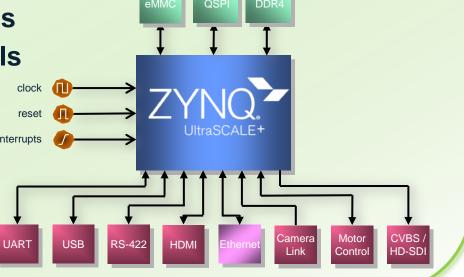

#### FPGA hardware

- ► Spartan Artix

- Kintex Virtex

- Zynq

- ▶7000 7000S

- Zynq UltraSCALE+

- ► Dual A53 / Dual R5

- Quad A53 / Dual R5 / Codec

- Quad A53 / Dual R5 / GPU

#### **▶** Tools

- Vivado HLx

- Matlab

- ...

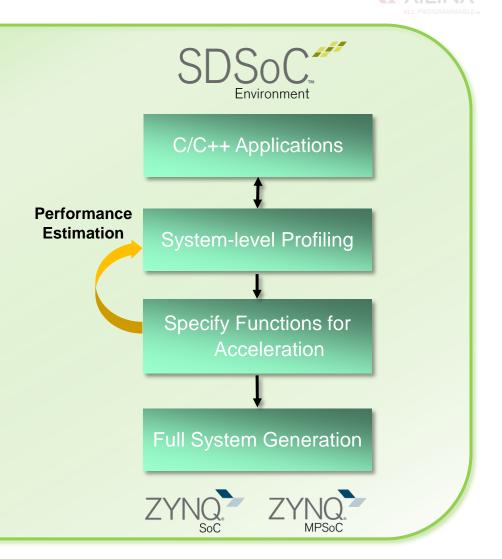

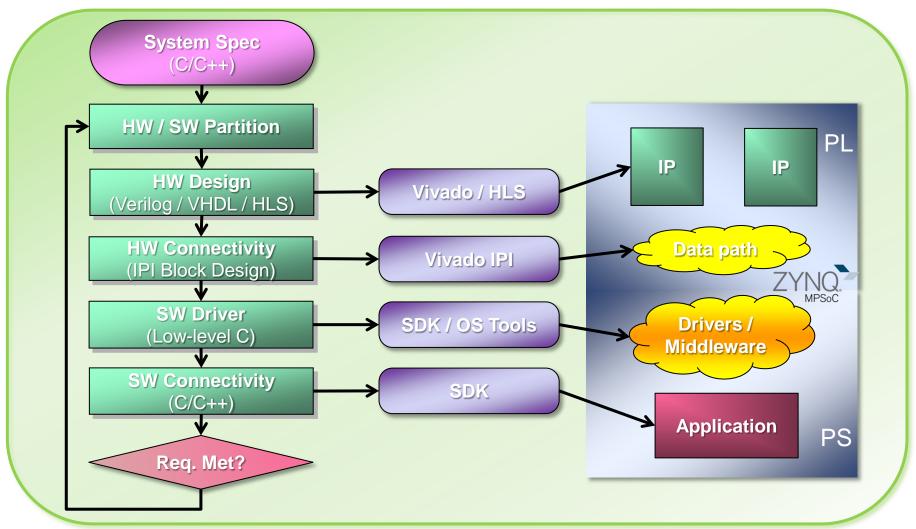

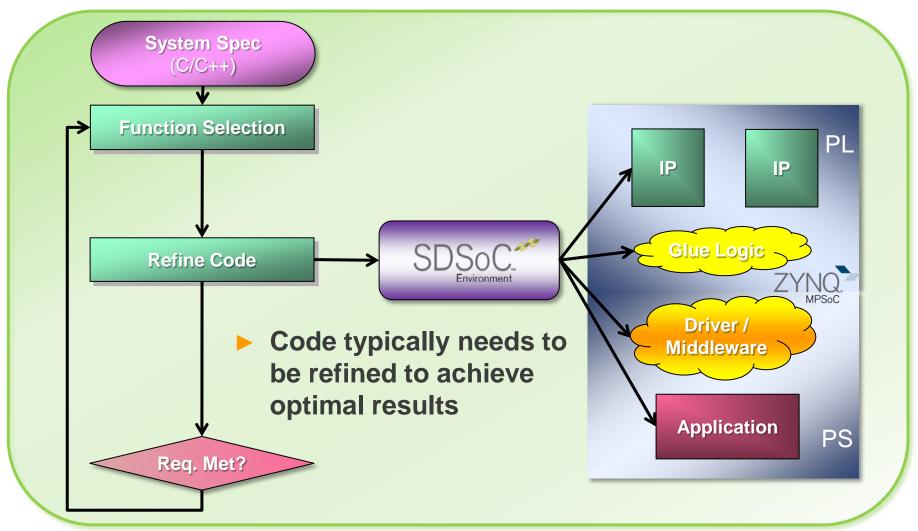

# Embedded Design Flow with SDSoC

- Migrate C/C++ functions to hardware

- System-level debug and profile

- Simple hardwaresoftware partitioning

- Full system generation including driver and hardware connectivity

#### Design Flow without SDSoC

#### Design Flow with SDSoC

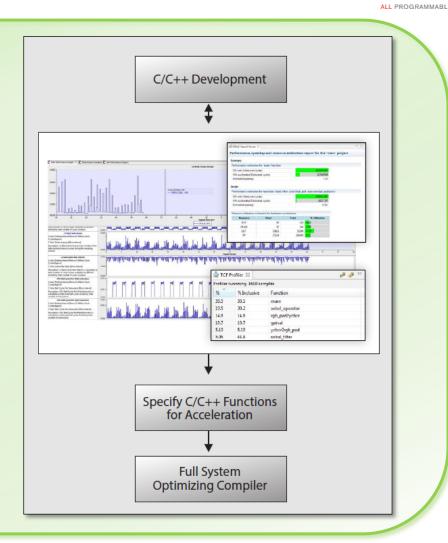

## **SDSoC System Level Profiling**

- Rapid system performance estimation

- Full system estimation (programmable logic, data communication, processing system)

- Reports SW/HW cycle level performance and hardware utilization

- Automated performance measurement

- Runtime measurement by instrumentation of cache, memory, and bus utilization

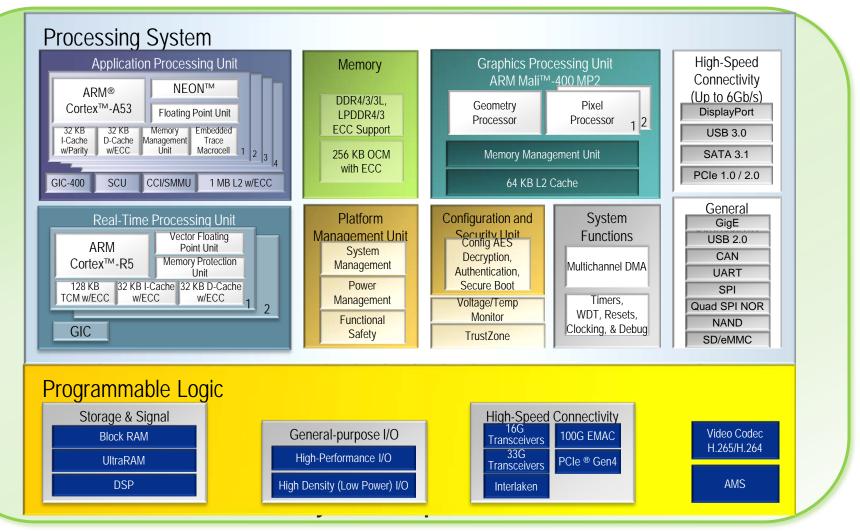

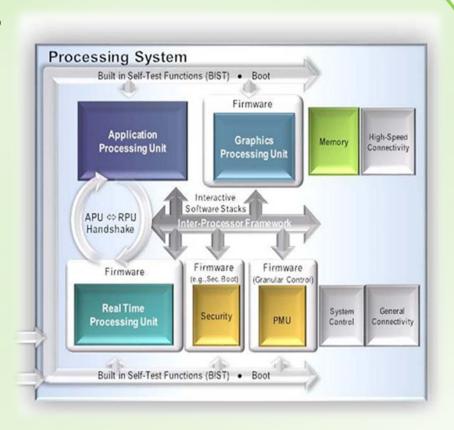

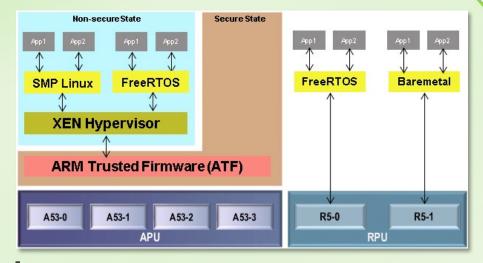

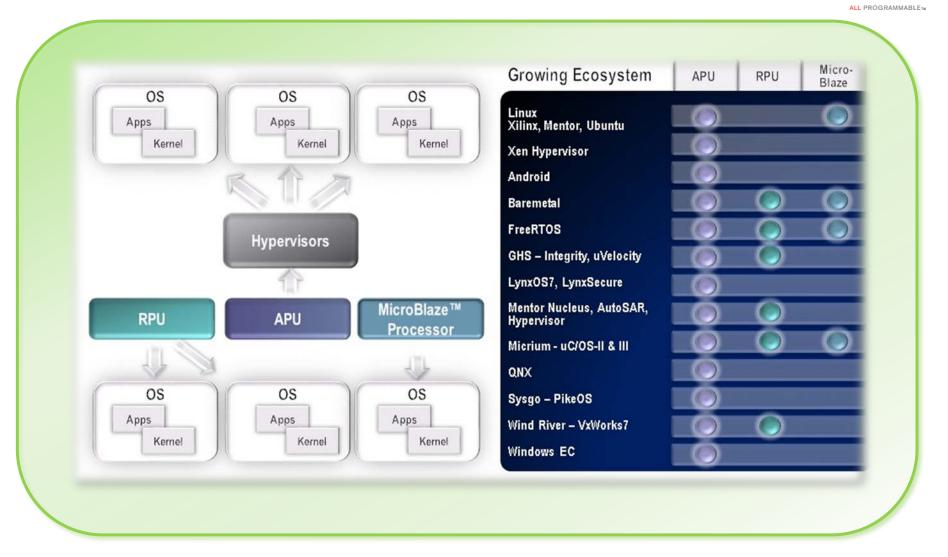

#### MPSoC HW/SW Considerations

- Quad-core ARM Cortex-A53

- Dual-core ARM R5

- ARM Mail-400MP GPU

- DDRx and SMC controllers

- Security firmware

- Platform Management Unit

- ► FSBL, uBoot

- ARM trusted firmware

- XEN hypervisor

- Software test libraries

- Inter-processor Framework

- Multi-OS boot image

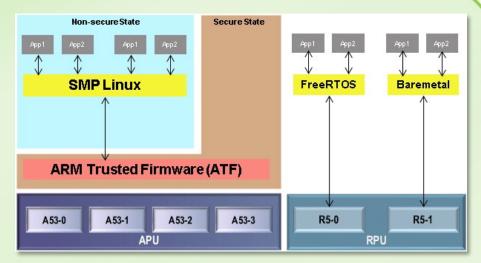

### **Example Default Configuration: APU-Linux / RPU**

- **System software**

- FSBL: First Stage **Boot Loader**

- **uBoot: Open source**

- APU: Non-secure mode

- ARM trusted firmware: From Xilinx, verified on APU

- SMP Linux

- No hypervisor: Non-secure mode

- RPU

- In split mode (default)

- **R5-0: FreeRTOS**

- R5-1: Bare-metal

# **Example Configuration: APU-Hypervisor Linux / RPU**

- System software

- FSBL: First Stage Boot Loader

- uBoot: Open source

- ► APU: Non-secure mode

- ARM trusted firmware/XEN hypervisor, verified on APU

- Guest OS

- Domain (1): Linux

- Domain (2): Bare-metal

- ► RPU

- In split mode (default)

- ► R5-0: FreeRTOS

- R5-1: Bare-metal

#### **Run-Time Software**

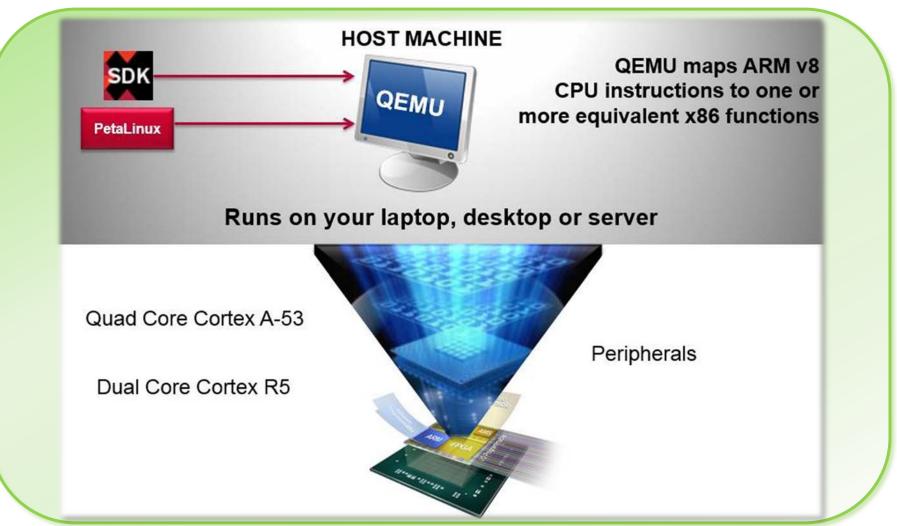

#### **Qemu Emulation Platform**

- QEMU emulation platform

- Provides Linux hosted emulation platform

- Accelerates and scales embedded software development

- Enables architecture and porting of software

- Emulates multiple blocks of the processing system

- QEMU enables you to start working on designs before hardware is available

#### **How Qemu Works**

## Core Vision

#### **Our competences**

Core|Vision has more than 125 man years of design experience in hard- and software development. Our competence areas are:

- System Design

- FPGA Design

- Consultancy / Training

- Digital Signal Processing

- Embedded Real-time Software

- App development, IOS Android

- Data Acquisition, digital and analog

- Modeling & Simulation

- PCB design & Layout

- Doulos & Xilinx Training Partner

## Q&A

Cereslaan 10b 5384 VT Heesch (1) +31 (0)412 660088

> www.core-vision.nl Email: info@core-vision.nl

# Single Device Devic

# CORE VISION EMBEDDED DEVELOPMENT

- FFUA DESIGN

- SYSTEM DEVELOPMENT

- DEDICATED ELECTRONICS

- EMBEDDED SOFTWARE

- DESIGN SERVICES

- MODELING AND SIMULATION

# Visit our booth 11

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT

| Essentials of FPGA Design                           | 1 day  |

|-----------------------------------------------------|--------|

| Designing for Performance                           | 2 days |

| Advanced FPGA Implementation                        | 2 days |

| Design Techniques for Lower Cost                    | 1 day  |

| Designing with Spartan-6 and Virtex-6 Family        | 3 days |

| Essential Design with the PlanAhead Analysis Tool   | 1 day  |

| Advanced Design with the PlanAhead Analysis Tool    | 2 days |

| Xilinx Partial Reconfiguration Tools and Techniques | 2 days |

| Designing with the 7 Series Families                | 2 days |

| Designing | FPGAs Using the | e Vivado Design Suite 1 | 2 days |

|-----------|-----------------|-------------------------|--------|

|           |                 | <u> </u>                |        |

- Designing FPGAs Using the Vivado Design Suite 2 2 days

- Designing FPGAs Using the Vivado Design Suite 3

2 days

- Designing FPGAs Using the Vivado Design Suite 4

2 days

- Designing with the UltraScale and UltraScale Architecture 2 days

- Vivado Design Suite for ISE Software Project Navigator User 1 day

- Vivado Design Suite Advanced XDC and Static Timing Analysis for ISE Software User2 days

| <b>&gt;</b> | Designing with Multi Gigabit Serial IO                   | 3 days |

|-------------|----------------------------------------------------------|--------|

|             | High Level Synthesis with Vivado                         | 2 days |

|             | C-Based HLS Coding for Hardware Designers                | 1 day  |

|             | C-Based HLS Coding for Software Designers                | 1 day  |

|             | DSP Design Using System Generator                        | 2 days |

| <b></b>     | Essential DSP Implementation Techniques for Xilinx FPGAs | 2 days |

| <b> </b>    | Embedded Systems Design                              | 2 days   |

|-------------|------------------------------------------------------|----------|

| <b>&gt;</b> | Embedded Systems Software Design                     | 2 days   |

| <b>&gt;</b> | Advanced Features and Techniques of SDK              | 2 days   |

| <b>&gt;</b> | Advanced Features and Techniques of EDK              | 2 days   |

| <b>&gt;</b> | Zynq All Programmable SoC Systems Architecture       | 2 days   |

| <b>&gt;</b> | Zynq All Programmable SoC Accelerators               | 1 day    |

| <b>&gt;</b> | C Language Programming with SDK                      | 2 days   |

| <b>&gt;</b> | Embedded Design with PetaLinux Tools                 | 2 days   |

| <b>&gt;</b> | Zynq UltraScale+ MPSoC for the System Architect      | 2 days   |

| <b>&gt;</b> | Embedded C/C++ SDSoC Development Environment and Met | hodology |

|             |                                                      | 1 day    |

|             |                                                      |          |

Land Market

| VHDL Design for FPG. | A |

|----------------------|---|

|----------------------|---|

Advanced VDHL

Comprehensive VHDL

Expert VHDL Verification

Expert VDHL Design

Expert VHDL

Essential Digital Design Techniques

| 3 | days |

|---|------|

|---|------|

2 days

5 days

3 days

2 days

5 days

2 days