# **Subjects**

- O JTAG Technologies (Rik Doorneweert, Area Manager)

- JTAG Technologies B.V. activities

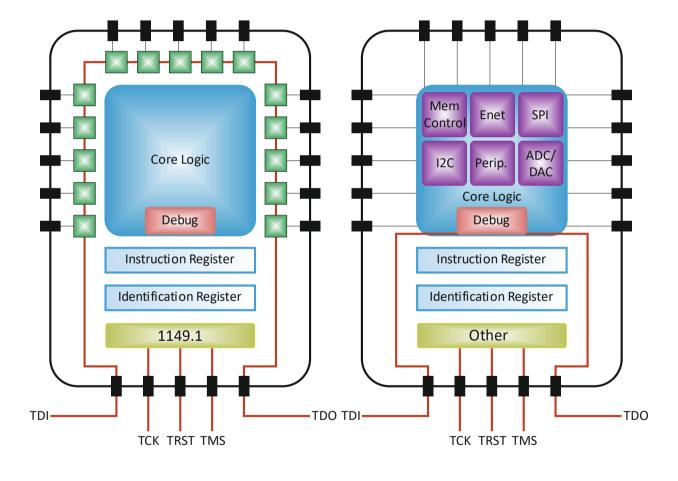

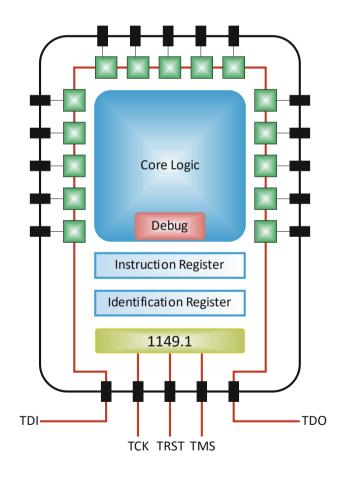

- O Introduction to (classic) Boundary Scan

- O Grass Valley Breda(Camera division) (Khaled Sarsam, Test Automation Architect)

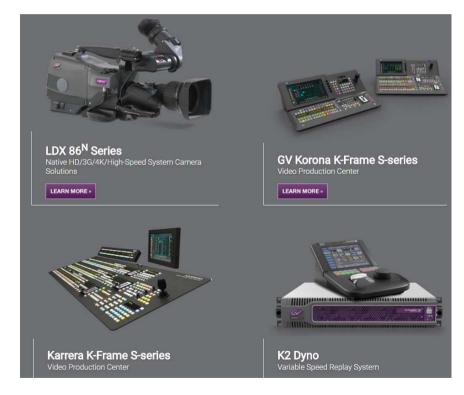

- About Grass Valley and it's products

- Embedded at-speed testing without the functional Firmware

- Embedded testing examples using JTAG interface

2

# JTAG Technologies B.V.

- Worldwide active since 1994, HQ in Eindhoven, 55 employees

- JTAG based tools for:

- o HW Engineers:

o Test Engineers:

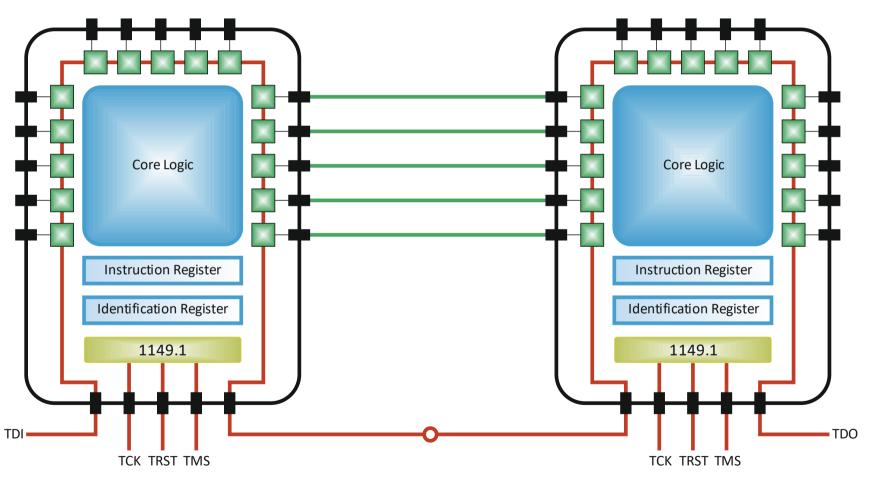

#### **Extest Interconnection test**

## Extest Memory connection test

#### Requires access to:

- Address bus

- Data bus

- Control signals

#### Examples:

- SRAM

- DRAM

- SDRAM

- DDR2

- DDR3

- DDR4... www.jtag.com

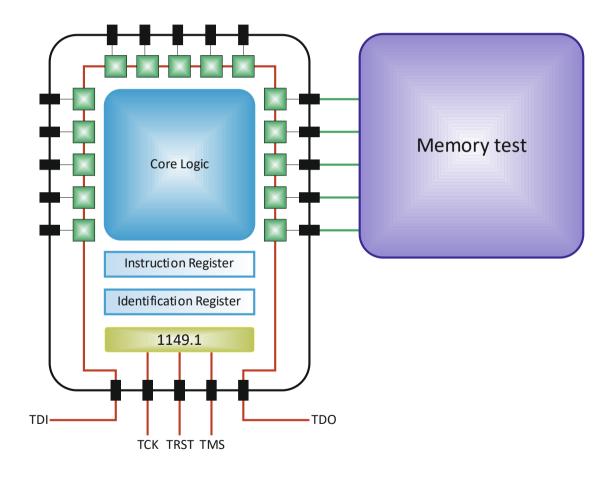

#### Intest

- BIST (Built In Self Test)

- Measure voltages (Zynq/XADC)

- Everything what is supported by the 1149.1 Device

5 www.jtag.com

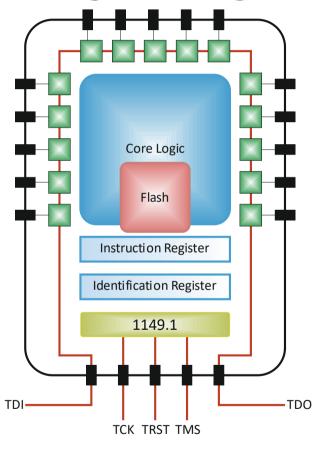

# Programming Embedded Flash

- Analog Devices

- Atmel

- Cypress

- Freescale

- Infineon

- Microchip

- Nordic

- NXP

- Philips

- Renesas

- ST

- Silicon Labs

- TI

6

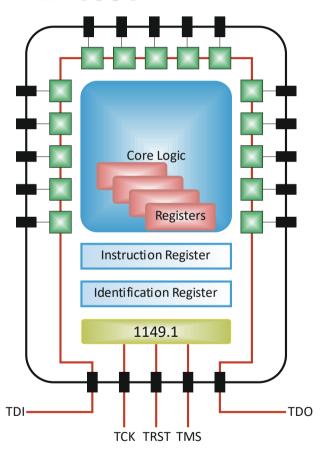

#### Emulative accessible uC's

- ARM

- Analog Devices

- Freescale

- Infineon

- Microchip

- Texas Instruments

- Xscale

- NXP

- ST

#### Emulative accessible FPGA's

- Altera, JTAG Translator

- Xilinx, JTAG Translator

# Grass Valley a Belden brand

#### Number of employees:

- o Grass Valley 1200+

- O Belden 8500+ (GV Included)

#### **Products:**

**Grass Valley**

Live ProductionEquipment

# **Test Automation**

Various interfaces at our disposal

- □ JTAG

- □ 12C

- ☐ SPI

- etc

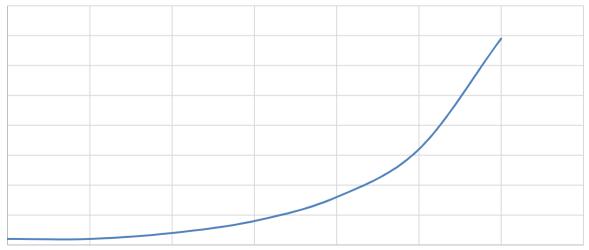

# Why test @ speed

- ☐ Almost reflecting the functional stage

- ☐ Cover production faults which might only occur at functional speeds

- Find faults at an early stage of the process (both development and production process)

Costs of resources at different test-phases in case fault is detected

# The JTAG interface @ Grass valley Breda

- ☐ Used for board-level testing part of our LabView based tests

- ☐ Automatic test-pattern generation using ATE tools

- ☐ Automatic flash-programming using bus-emulation

- ☐ Now also used for Embedded testing (At-speed)

- ☐ Test Automation using Python scripting

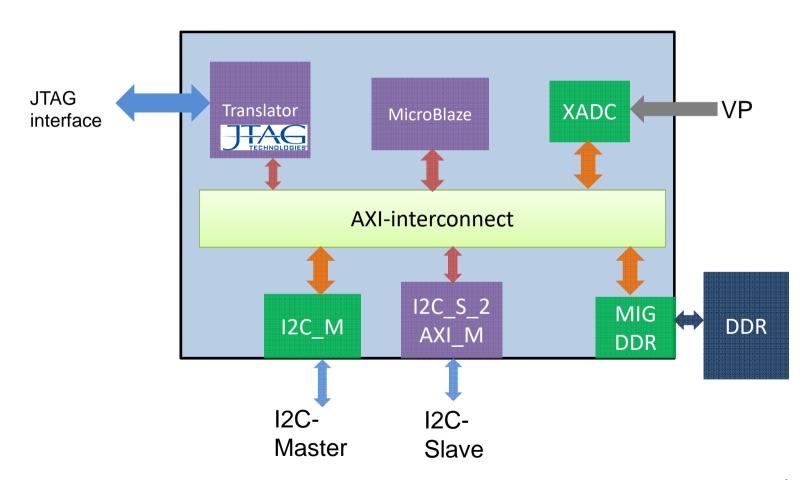

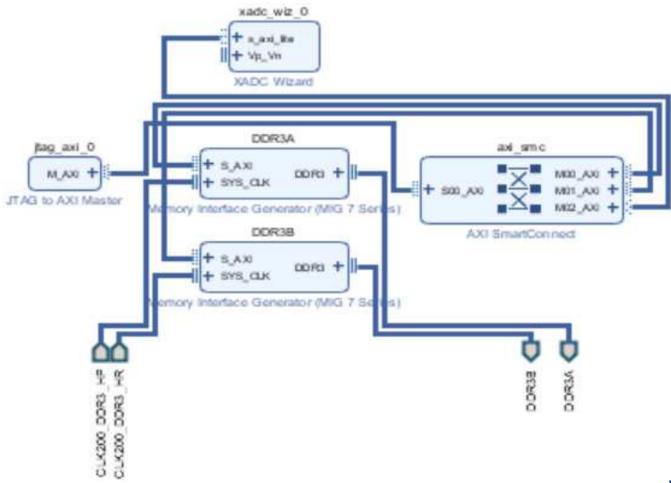

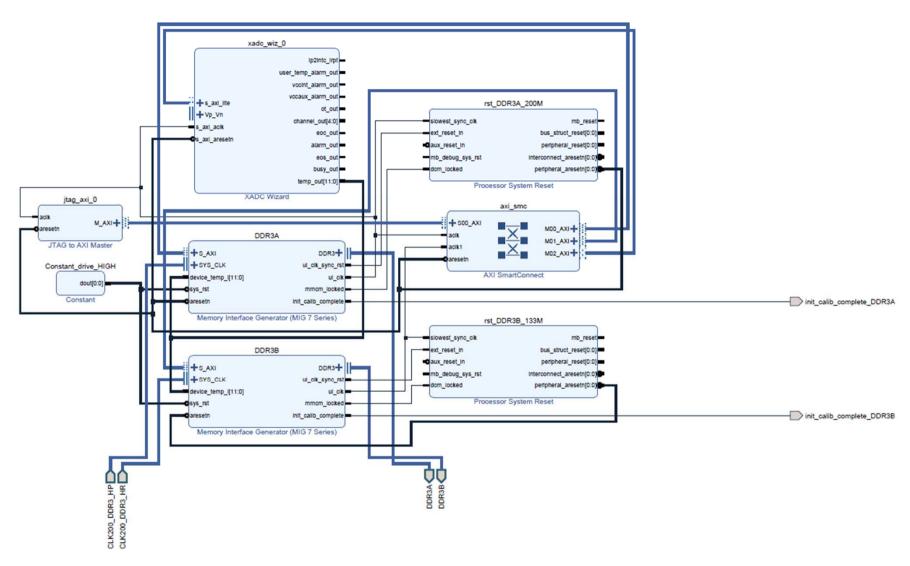

#### Example 1: FPGA based @Speed DDR3-interconnection test

#### Generation sequence

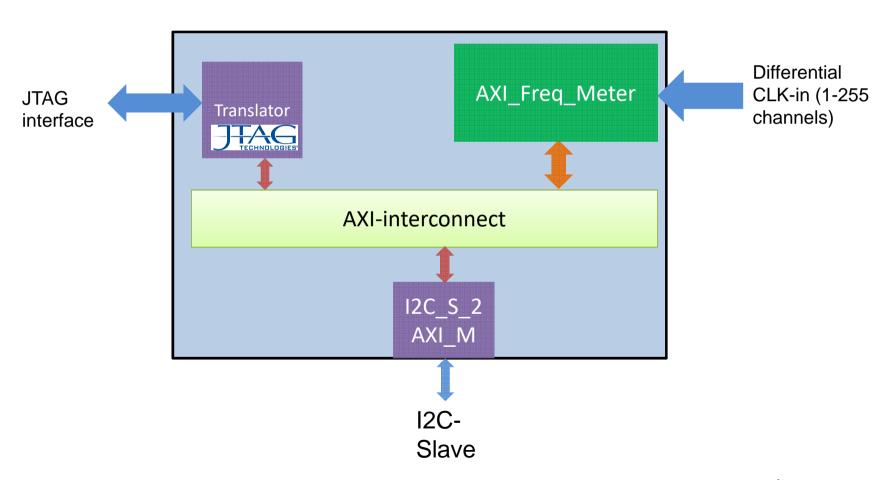

- ☐ AXI-interconnect based FPGA design with JTAG Translator as bus-master

- ☐ Compile & generate an SVF-file

- ☐ Generate At-speed test using CTPG\_M (JTAG Technologies)

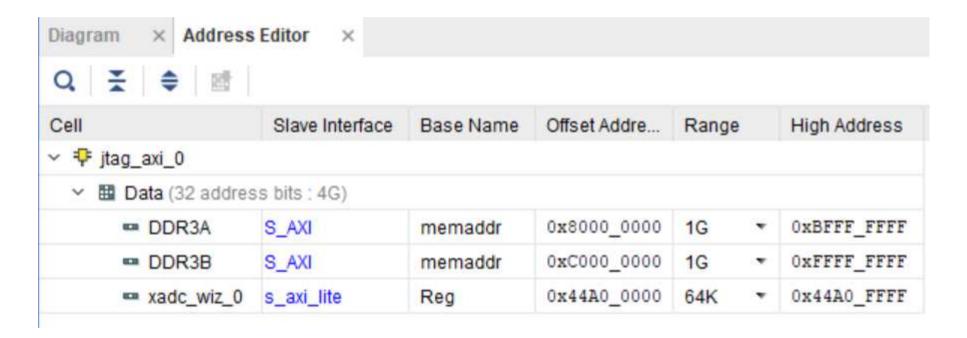

# Vivado FPGA design DDR-memory

### FPGA Design System Memory-map

#### Test sequence

- ☐ Load the FPGA-design on-the-fly using JTAG Interface (SVF)

- ☐ Wait for Config\_done = 1

- ☐ Wait for ddr\_calib\_done=1

- Execute AT-speed test (ProVision, JTAG Technologies)

- ☐ If fail: execute boundary-scan diagnostics (BSD, JTAG Technologies)

#### Example 2: Embedded Frequency-measurement

# Again system memory-map

| ✓ ■ AXI (32 address) | s bits : 4G) |     |             |     |   |             |

|----------------------|--------------|-----|-------------|-----|---|-------------|

| Frequency            | S_AXI        | Reg | 0x4000_0000 | 64K | * | 0x4000_FFFF |

| SelectCh             | S_AXI        | Reg | 0x4001_0000 | 64K | * | 0x4001_FFFF |

# Python script

```

import jft

import jftuproc

import time

jftuproc.Init("Kintex7","","IC7")

jftuproc.EnterDebug()

freq sel address =

0x40010000

measure address =

0x40000000

jftuproc.WriteMemory(0x40010000,0x01)

jftuproc.WriteMemory(0x40010000,0x00)

def MeasureChannel (channel):

jftuproc.WriteMemory(freq sel address, channel)

val = jftuproc.ReadMemory(measure address)

return val

for channel in range (0,8):

measuredfreg = MeasureChannel(channel)

print("channel", channel, ":", measuredfreq)

```

#### Executed python-script's output

```

Initializing Jft ...

channel 0 : 74187415

channel 1 : 222562247

channel 2 : 148374831

channel 3 : 148374831

channel 4: 200032982

channel 5 : 200032983

channel 6: 24579839

channel 7 : 0

Closing Jft...

Script ended successfully.

Console

Problems

```

#### **Benefits**

- ☐ Easy test integration using our the JTAG Technologies

- controllers which we already have for years

- ☐ Easy test automation using scripting (Python, TCL)

- ☐ Faster time-2-market

# Questions?