## Design Challenges for Testing High Speed Serial Communications

Design Automation & Embedded Systems 2018 John Marrinan, Director Application Engineers 7<sup>th</sup> and 8<sup>th</sup> of November, 2018

### DESIGN AUTOMATION & EMBEDDED SYSTEMS

FPGA - SECURITY - INTERNET OF THINGS - ELECTRONIC DESIGN & PRODUCTION - EMBEDDED - DESIGN FOR EXCELLENCE - EMBEDDED DESIGN CHALLENGES

7 NOV TECHNOPOLIS, MECHELEN 8 NOV VAN DER VALK HOTEL, EINDHOVEN

## AGENDA

- Serial Data Link Challenges

- Fundamentals of Serial Data Link Analysis

- Measurement System De-embedding

- Practical Channel Emulation PCIe Gen3

- Practical Receiver Equalization

8 NOVEMBER 2018

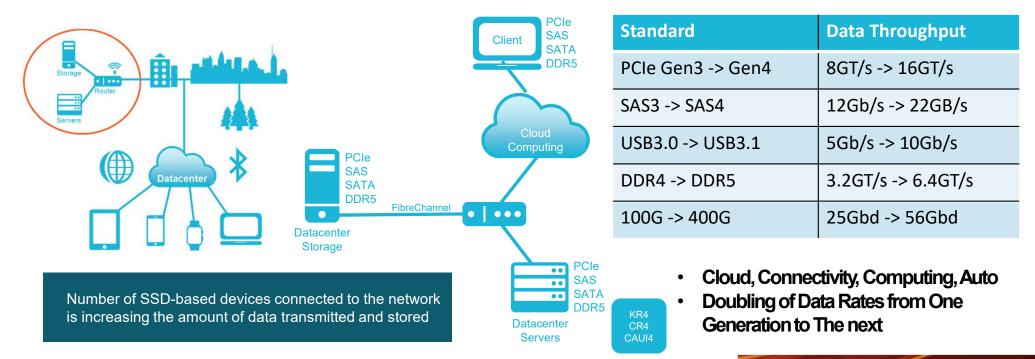

## Next Generation Serial Standards

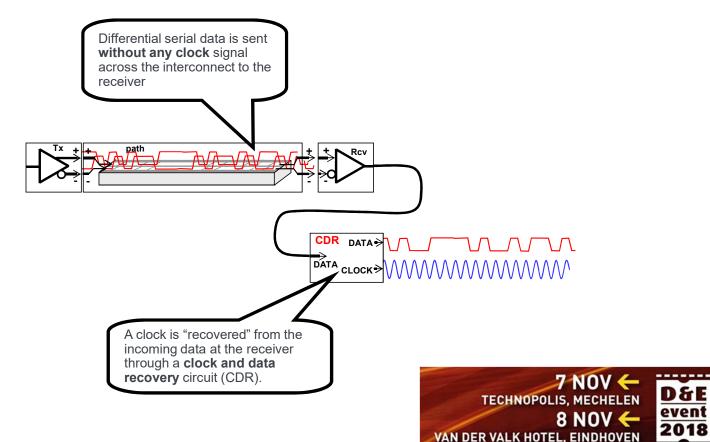

## Design and Test Challenges Transmission Path of a High Speed Serial

**Ideal State**

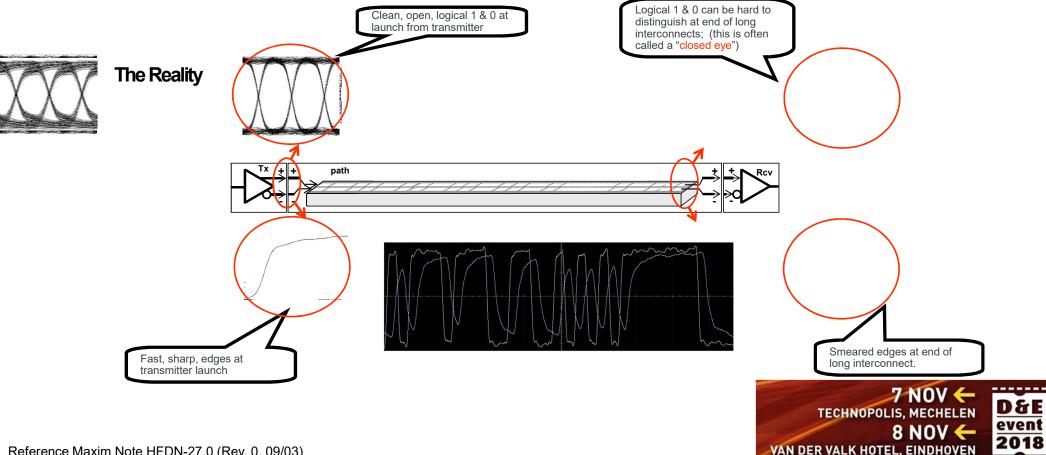

## **Design and Test Challenges** Transmission Path of a High Speed Serial

Reference Maxim Note HFDN-27.0 (Rev. 0, 09/03)

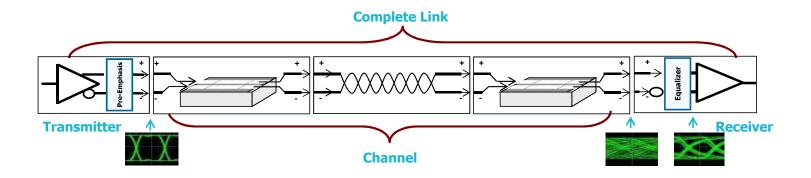

## Anatomy of a Serial Data Link

Aspirational goal: 0 errors Practical Goal: Bit Error Rate < Target BER

Since BER is the ultimate goal, why not measure it directly?

### Serial Data Link Integrity = Bit Error Ratio

- Bit Error Ratio Testers (BERTs) are the tools for measuring BER directly

- Why not use ONLY BERTs for Serial Data Link Analysis?

- **Difficult to model/emulate the equalizer**

- □ Measurements can take a very long time

- □ Instruments are very expensive and not all that flexible

- Does not analyze the root causes of the impairments of the links

- Alternative approach: use a scope and advanced jitter and noise analysis tools

- □ Easily move from Compliance to Debug

- □ Better equipped to identify root causes of eye closure

- **□** Equalizer can easily be modeled

- □ More cost effective

- □ Greater throughput

#### BER requirements have been translated to Jitter (and more recently, Noise) budgets

| Characteristic                | Units | Minimum                       | Nominal | Maximum     | Reference |

|-------------------------------|-------|-------------------------------|---------|-------------|-----------|

| Tx RJ <sup>b c d</sup>        | UI    | 0.135 e                       | 0.150 f | 0.165 9     | 5.8.4.6.1 |

| Tx SJ <sup>c</sup>            | UI    | See figure 129 and figure 130 |         | 5.8.5.7.4.5 |           |

| WDP at 6 Gbps b h             | dB    | 13                            |         | 14.5        |           |

| NEXT offset frequency i j k   | ppm   | 2 500                         | -       |             |           |

| Total crosstalk amplitude i k | mVrms | 4                             |         |             |           |

| Receiver device configuration |       |                               |         |             |           |

<sup>a</sup> For a characteristic with only a nominal value, the test setup shall be configured to be as close to that value as possible while still complying with other characteristics in this table.

For characteristics with minimum and maximum values, the test setup shall be configured to be within the range specified by the minimum and maximum values. The range shall not be used to define corner test conditions required for compliance

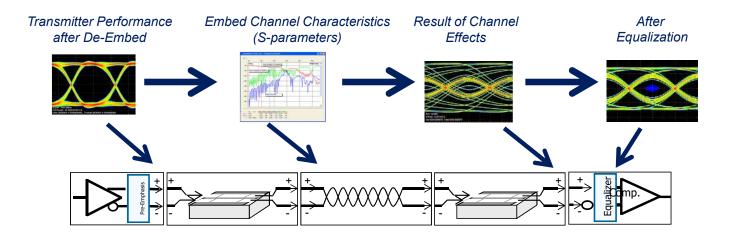

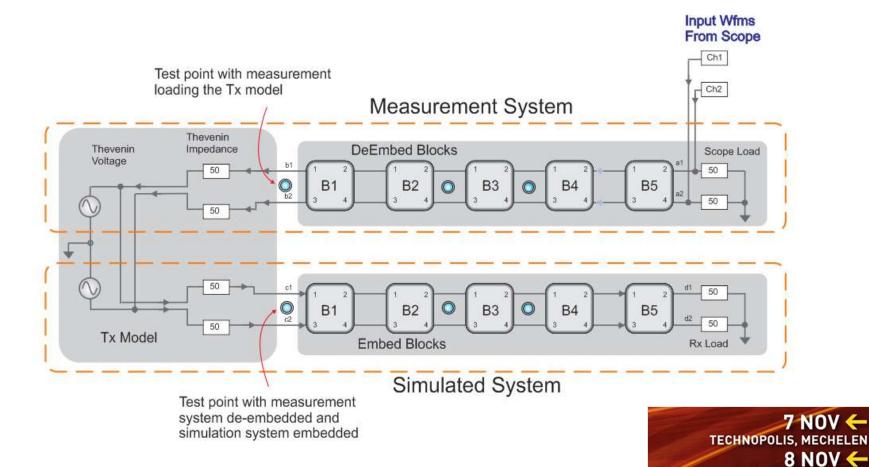

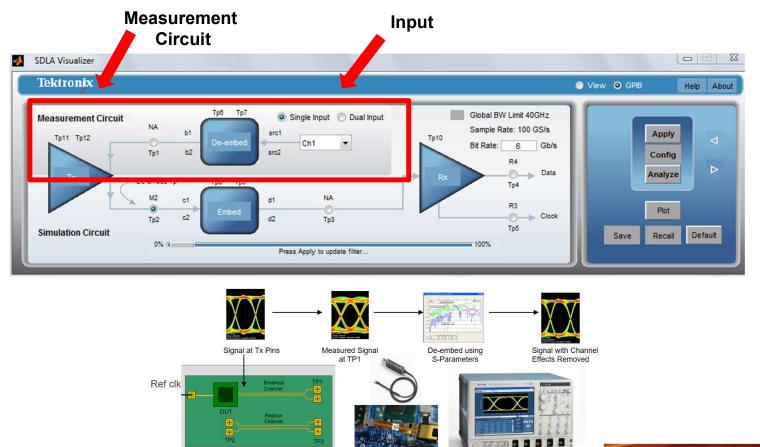

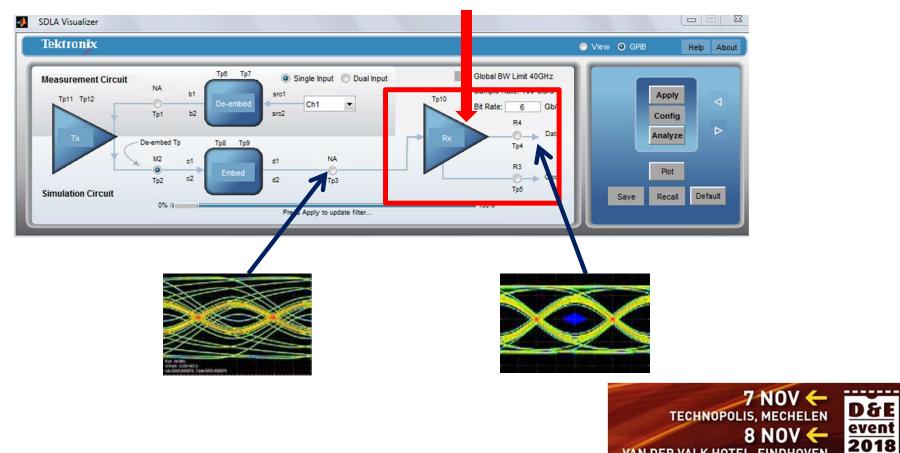

### Fundamentals of Serial Data Link Analysis

- De-embed measured circuit as needed, to remove the effects of the test fixture, cables and/or the channel to characterize the Transmitter

- *Embed* the simulation circuit: observe the waveform at the receiver pins

- Emulate the *Equalization* inside the Rx: observe the waveform at the comparator

1**%**8/2018

### SDLA Tool Set Have Two Components

.....

D&E

event

2018

VAN DER VALK HOTEL, EINDHOVEN

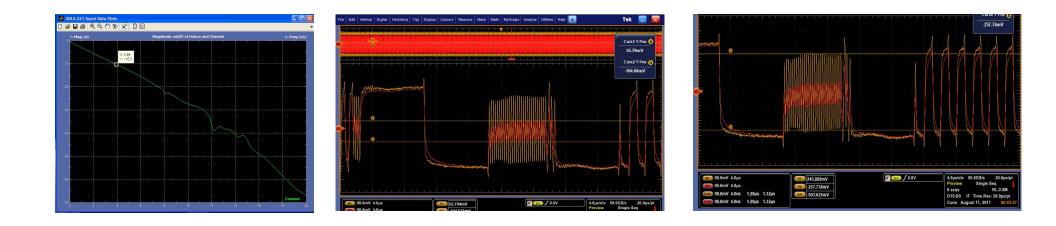

## De-embedding Test Equipment Effects

### *De-Embed* the Measurement Circuit – Coax Cables

- Removal of the effects of measurement equipment is required and necessary for many next generation standards

- Compensating for loss and reflections due to the measurement circuit is required

- The example below shows an 8Gb/s signal before and after the removal of SMA cables

Before De-Embedding 7.6363ps 34.210ps -33.590ps TIE (Source), Source 2.5803fs 3.9522fs 7.5103ps 33.210ps -32.6470 659 00mV 0.00001/ 659 00ml 658.00n 0.0000 After De-Embedding Eye Height ~715mV

11/8/2018

Eye Height

~660mV

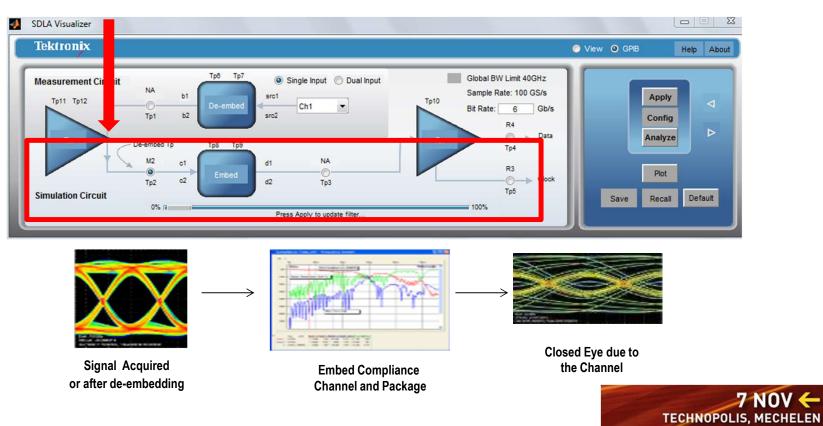

## Embedding Channel Effects

#### Simulation Circuit

D&E

event

2018

8 NOV ←

VAN DER VALK HOTEL, EINDHOVEN

### Fundamentals of Serial Data Link Analysis Example using PCI Express 3.0

**Signal Acquired** from Compliance Board

Embed the Add-In Card Closed Eye due to **Compliance Channel** the Channel

for Long Channel

Open Eye for **Measurements**

| System Board Eye Limits                |          |              |          |  |

|----------------------------------------|----------|--------------|----------|--|

| Parameter                              | Min      | Max          | Units    |  |

| V <sub>TXS</sub><br>V <sub>TXS_d</sub> | 34<br>34 | 1200<br>1200 | mV<br>mV |  |

| T <sub>TXS</sub>                       |          | 41.25        | ps       |  |

Add-In Card Eye Limits <sup>1</sup>

| Parameter                              | Min      | Max          | Units    |

|----------------------------------------|----------|--------------|----------|

| V <sub>TXA</sub><br>V <sub>TXA_d</sub> | 50<br>50 | 1200<br>1200 | mV<br>mV |

| T <sub>TXA</sub>                       |          | 41.25        | ps       |

11/8/2018

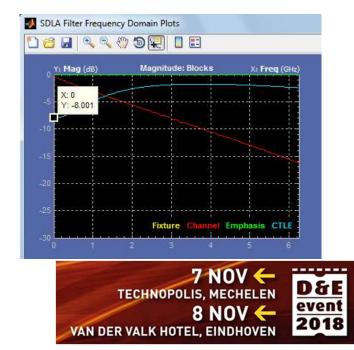

### Embed Simulation Circuit (Compliance Channel)

- Verifying the effects on the waveform are correct can be done by looking at the S-parameters of the channel model

- Based on the PCIe 3.0 Add-In Card Compliance Channel, 10dB (0.3 voltage) attenuation is expected on high frequency bits (4GHz for PCIe Gen 3)

11/8/2018

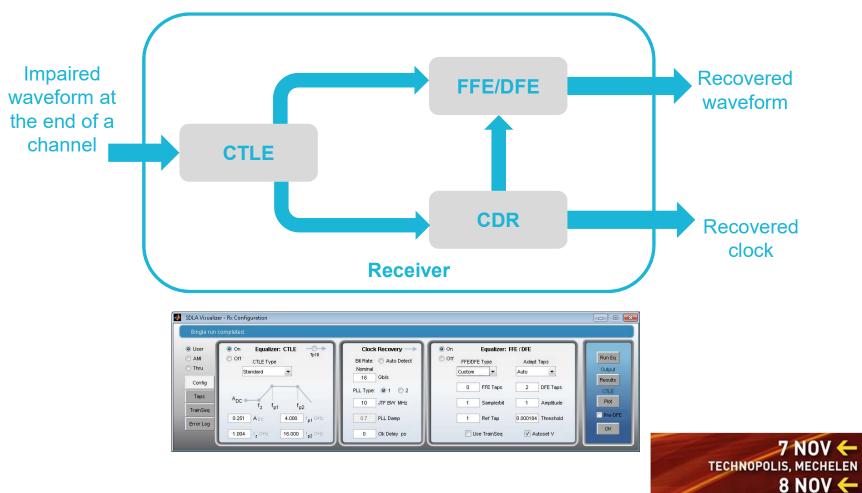

## Rx Equalization Create TP2' Eye

Simulation Circuit

VAN DER VALK HOTEL, EINDHOVEN

D&E

event

2018

VAN DER VALK HOTEL, EINDHOVEN

## Apply Receiver Equalization

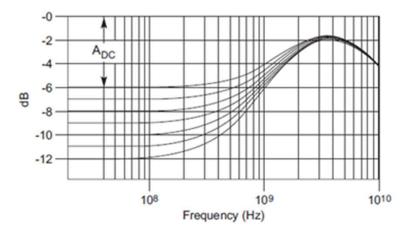

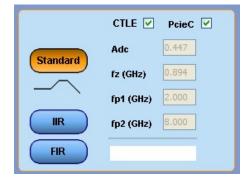

- Equalizer is optimized on the CTLE + DFE tap value that results in the best eye area

- 8dB (~60% attenuation) Adc settings are shown in the example below

- PCIe reference equalizer is CTLE and 1 Tap DFE

- CTLE one Zero and Two Poles

- DFE 1 Tap (-20/20mV tap value)

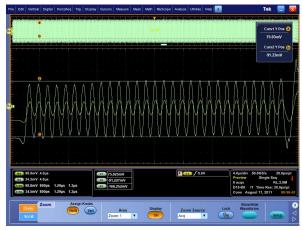

### Validate CTLE EQ Analyze Raw and CTLE EQ Waveform

- Measure the low frequency content of the signal on the acquired waveform (Orange) 615mV approx.

- Based on the CTLE that was applied, we expect a 60% attenuation in the low frequency content after the CTLE 240mV

### Apply Receiver Equalization Validate Equalizer: Analyze DFE

- The DFE will open the eye by twice the tap value

- PCIe uses a 1 tap DFE, meaning that the previous bit will determine if change of the current bit.

- The table below outlines the change based on the 20mV Tap

- High frequency signal before DFE is 126mV and after 166mV, which is 2 times the tap value of 20mV

| Previous Bit | Current Bit | Change    |

|--------------|-------------|-----------|

| 0            | 1           | 20mV      |

| 1            | 0           | -20mV     |

| 0            | 0           | No Change |

| 1            | 1           | No Change |

## **Final Results**

### PCI Express Compliance Measurements

- PCIe CEM compliance measurements can now be made on the TP2' waveform (after the EQ and CDR stages). Better correlation with BER

- Simultaneous assessment of the signal at each point during the post processing stage

11/8/2018

### Summary

- Traffic Demands in Datacentres and Automotive Industries driving doubling in data rates.

- High Speed Serial Data Links Suffer Frequency Related Losses In Channels

- Test Equipment Utilising New Emulation Technics To address This

- DSP Technics In Oscilloscopes Are Used To Remove Non-Ideal Effects of Measurement Equipment Improving Margin

- Similar Techniques Are Used to Emulate The Effect of Channel Losses and Receiver Equalisation

- These Techniques, Plus The Ability To Incorporate Emulation and Models into Scope DSP Processing Allows Better Correlation Between the PHY later and BER performance

# Questions?

More information?

C.N.Rood <u>www.cnrood.com</u> Arthur Hartsuiker <u>ahartsuiker@cn</u> Sven de Coster <u>cdecoster@cnro</u> Tektronix: www.tek.com

### DESIGN AUTOMATION & EMBEDDED SYSTEMS

FPGA - SECURITY - INTERNET OF THINGS - ELECTRONIC DESIGN & PRODUCTION - EMBEDDED - DESIGN FOR EXCELLENCE - EMBEDDED DESIGN CHALLENGES

7 NOV TECHNOPOLIS, MECHELEN 8 NOV VAN DER VALK HOTEL, EINDHOVEN