# Todays challenges of controlled impedance design and material choice

By: Boy van Veghel

#

- 1988 Quality Products International did start (became QPI Group later on)

- Development Printed circuit technology

- Supply of printed circuits

- Multi-layer, Flex, Flex-rigid, Stretch

- Advanced materials and constructions

- PCB Design

- PCB Lay-out with Mentor, Cadence, Altium and Zuken software

- PCB Laboratory

- 2015 We became part of Fineline Global Ltd.

- One of the world leading PCB providers

- 2018 We changed our name to Fineline QPI BV and moved to new location in Panovenweg 12, Helmond

#### Impedance requirements

- More and more PCB's require Impedance control

- Increase in demand of data speed

- > Higher bit rates

- > Higher frequencies

- Technology drivers

- ➤ DDR 4 signals

- ➤ USB 3 signals

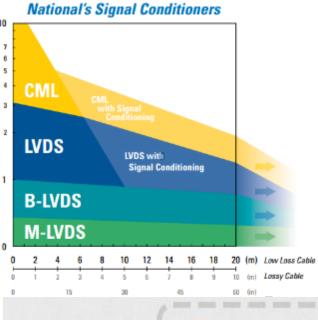

- >LVDS signals

- Material choice is becoming crucial

- $\rightarrow$  Dk(Er) and Df are very important

up to 480 Mbps

Theoretical speed up to 5Gbps (practical speed up to 300MB/s)

Theoretical speed up to 5Gbps (practical speed up to 300MB/s)

- Next-generation USB specification SuperSpeed USB

- Theoretical speed of 10Gbps (or 1.2GB/s)

#### What is impedance?

- o Impedance (Zo) is the sum of the resistance and reactance of an electrical circuit

- olt is measured in Ohms  $(\Omega)$

- Impedance is an alternating current characteristic in which signal frequency is an important element

- The longer the trace or the higher the frequency, the more imperative it becomes to control the trace impedance

- Signal frequency is a vital factor for traces which connect to components requiring two to three hundred MHz or more

### Controlled impedance on PCBs

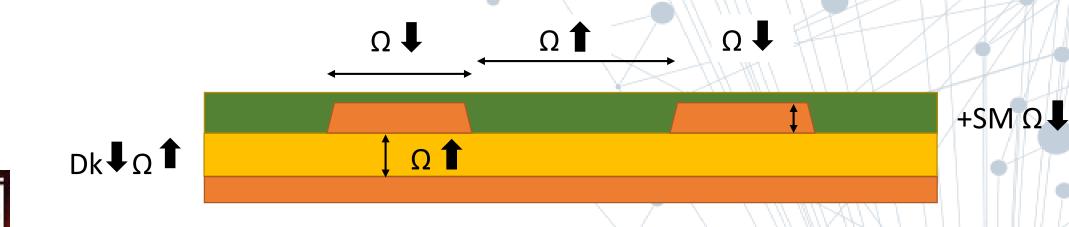

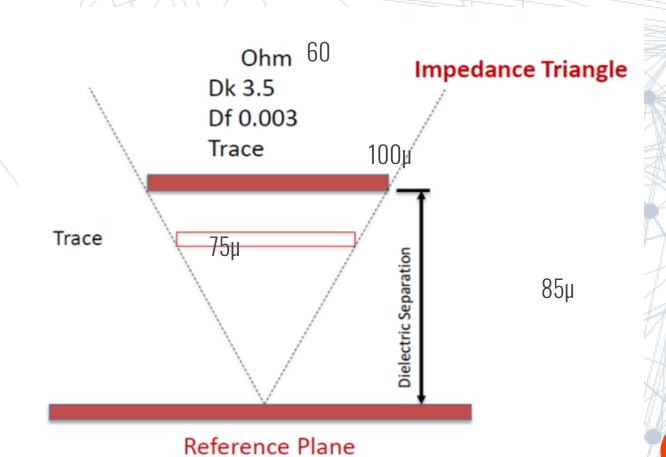

- The impedance is determined by

- ➤ Trace width, trace height

- ➤ Dielectric constant of the board material

- ➤ Distance to reference plane(GND)

- Some basic rules

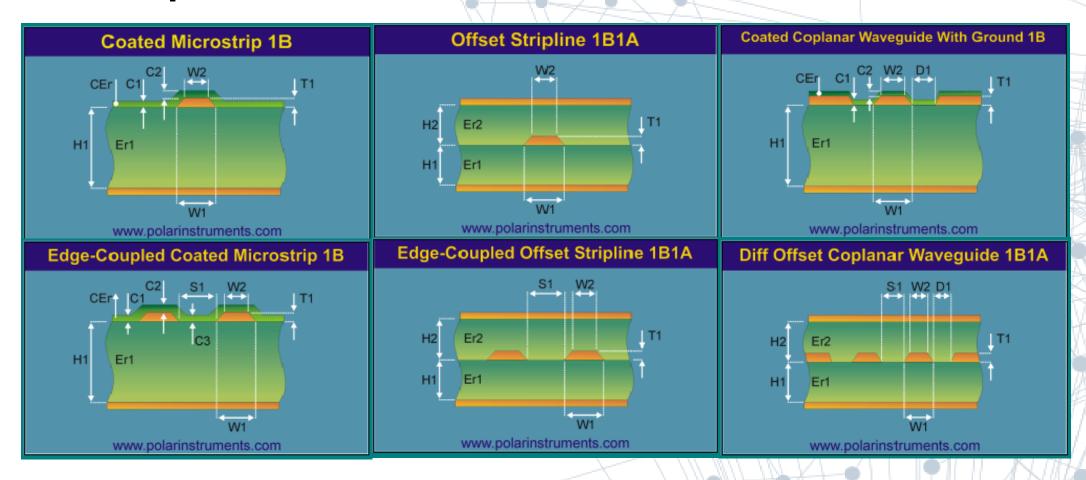

#### Common impedance models

Single ended

Differential

#### Common controlled impedance values

- $\circ$  Single ended impedance  $40\Omega$ ,  $45\Omega$ ,  $50\Omega$ ,  $55\Omega$ ,  $60\Omega$ ,  $75\Omega$

- $\circ$  Differential impedance  $80\Omega$ ,  $85\Omega$ ,  $90\Omega$ ,  $100\Omega$

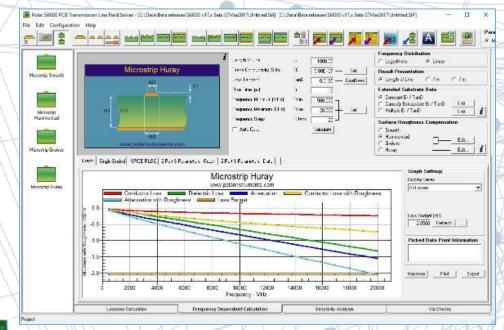

- Impedance at Fineline-QPI will be calculated using

- > Polar SI9000

- > Polar speedstack

- After production impedance will be verified

- Via a special designed test coupon on production panel

#### Design challenges

- Combination of low and high impedance

- $\triangleright$ e.g.  $40\Omega$ , and  $60\Omega$  single ended

- ightharpoonup e.g.  $80\Omega$  and  $100\Omega$  differential

- Require the opposite value

- ➤In trace width

- ➤In trace thickness

- ➤ In reference isolation to GND

#### Impedance calculation

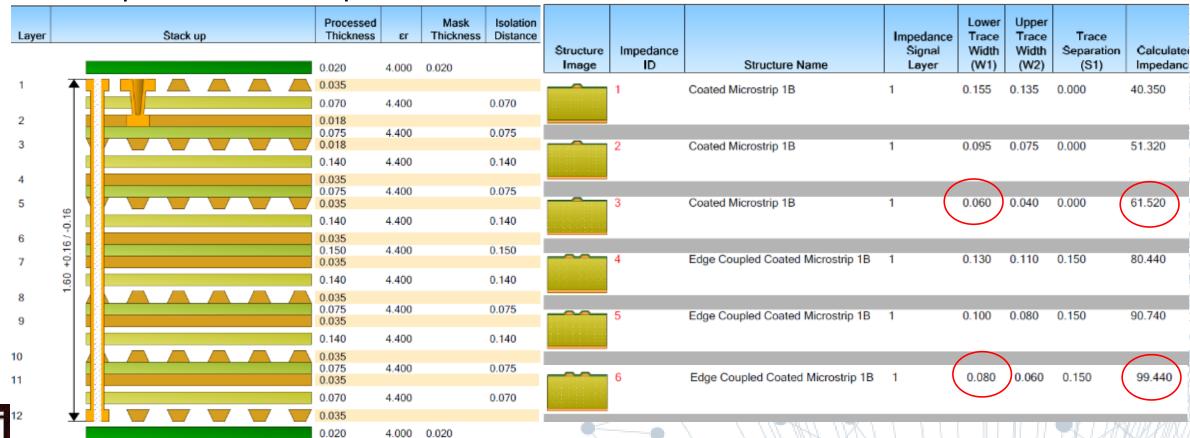

$\circ$  Example outer layer impedance of 40,50,60  $\Omega$  SE and 80,90,100  $\Omega$  Diff.

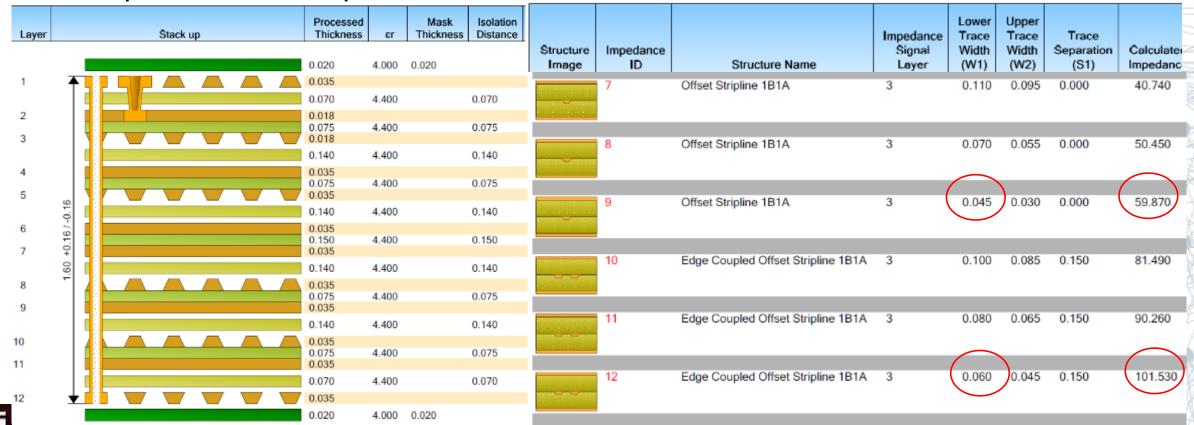

#### Impedance calculation

$\circ$  Example inner layer impedance of 40,50,60  $\Omega$  SE and 80,90,100  $\Omega$  Diff.

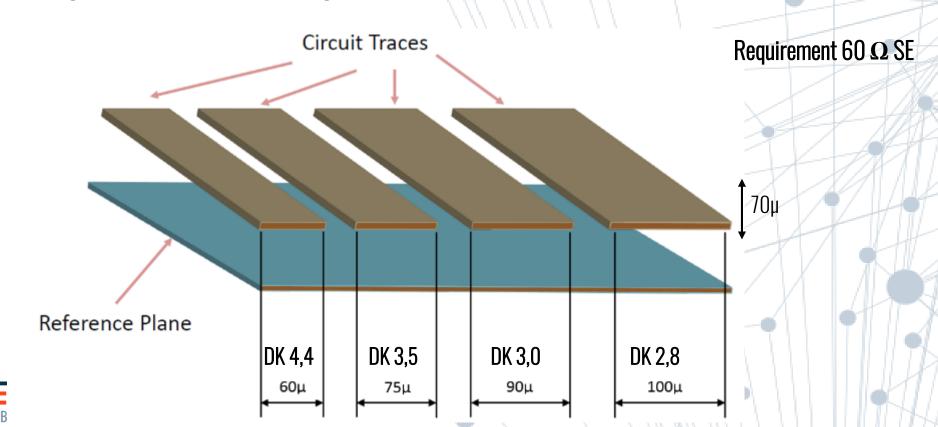

#### Design challenges

- Thinner/smaller traces = higher trace resistance = <u>lower system performance</u>

- ∘Traces <75µm

- > Will lower the yield in manufacturing

- > Price of the PCB will increase

- ➤ Lead-time will be longer

- Solution would be to lower the Dk

- O Lowering the Dk to e.g. 3,5 makes the track width go up to 75μm

- ➤ Better yield,

- **≻**Lower price

- ➤ Shorter leadtime

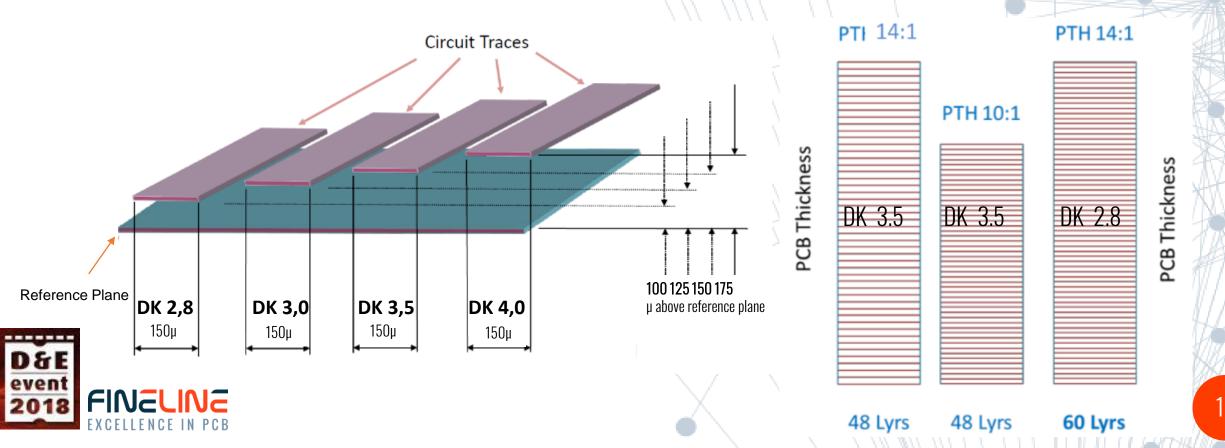

#### Low Dk material

D&E event 2018

- Using a low DK material has several advantages

- ➤ The trace width increases

- > Copper weights can increase for high current

#### Low Dk material

- The number of layers can be increased within the same thickness

- The thickness can be decreased to improve on aspect ratio

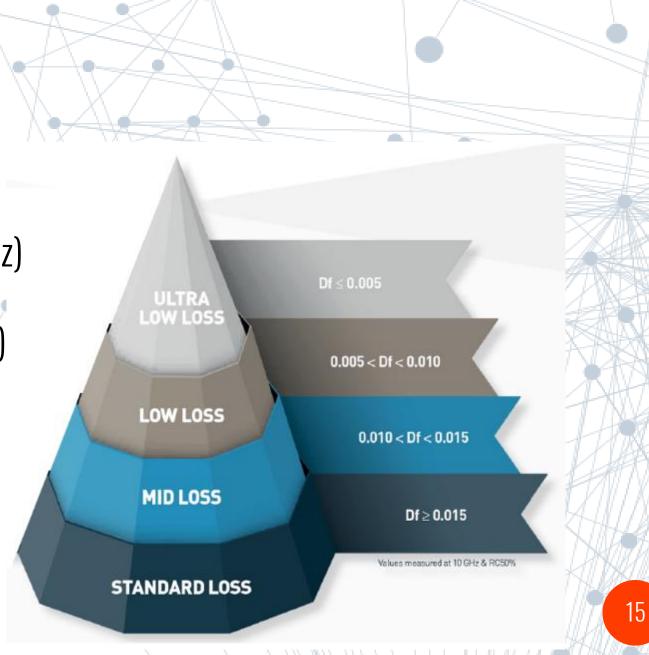

### Choosing the rigth material

- Key factors in choosing the right material for your design

- ➤ Dielectric contant (Dk)

- ➤ Dissipation factor (Df)

- ➤ Copper foil type

- ➤ Glass style

- A lot of different laminate manufactures offer a wide range of products

- ➤ Dk&Df are often given as an average value

- ➤ Every prepreg and laminate thickness has there own Dk&Df value

- These small differences can have a huge impact on controlled impedance lines and signal integrity

- Lead-times and MOV or MOQ varies from one to another

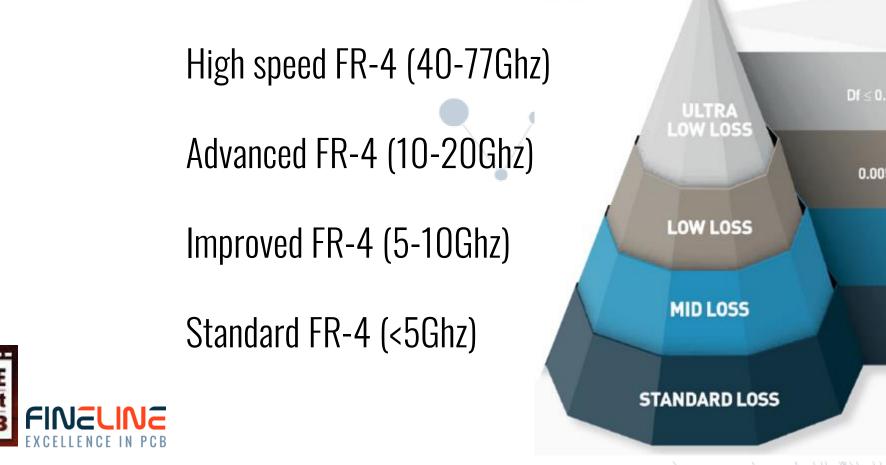

# Choosing the rigth material

Material vs frequency

> Depending on insertion loss

### Choosing the rigth material

$\circ$  Some examples

| Brand     | Туре        | Dk   | Df     |

|-----------|-------------|------|--------|

| Isola     | FR408HR     | 3,65 | 0,0095 |

| Panasonic | Megtron 6   | 3,61 | 0,004  |

| Isola     | I-Tera MT40 | 3,45 | 0,0031 |

| Ventec    | VT-464      | 3,5  | 0,013  |

| Nelco     | N4800-20SI  | 3,24 | 0,0064 |

| Ventec    | VT-462      | 3,05 | 0,0035 |

| Isola     | Astra MT77  | 3,00 | 0,0017 |

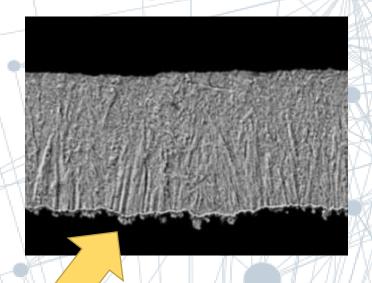

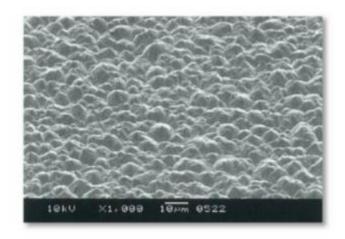

#### Copper foil

- The roughness of the copper foil has an effect on impedance and signal loss(Skin depth)

- Low profile copper foils gives the lowest loss

| Frequency | Skin Depth |  |

|-----------|------------|--|

| 10 MHz    | 21 µm      |  |

The current is able to tunnel below the surface profile and through the bulk of the conductor

| Frequency | Skin Depth |  |

|-----------|------------|--|

| 100 MHz   | 6.6 µm     |  |

The current is forced to follow every peak and trough of the surface profile increasing path length and resistance

| Frequency | Skin Depth<br>(Copper) |

|-----------|------------------------|

| 50 Hz     | 9.3 mm                 |

| 10 MHz    | 21 μm                  |

| 100 MHz   | 6.6 μm                 |

| 1 GHz     | 2.1 μm                 |

| 10 GHz    | 0.66 μm                |

#### Copper foil

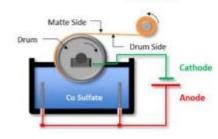

- There are two sorts of copper foils

- ➤ RA (Rolled annealed)

- ➤ ED (Electro deposited)

#### **Copper Foil Manufacturing Processes**

Rolled

VS

- Smoother

- Higher Cost

- Rougher

- Lower Cost

#### Copper foil

#### **Common Roughness Profiles**

#### **IPC Standard Profile**

IPC Very Low Profile(VLP)

Ultra Low Profile (ULP)Class

No min/max spec

-Other names: HVLP, VSP

- -No IPC spec

- -Typically < 2  $\mu$ m max

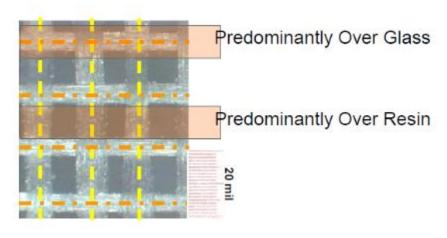

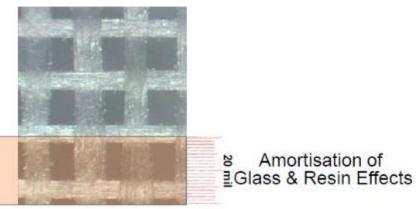

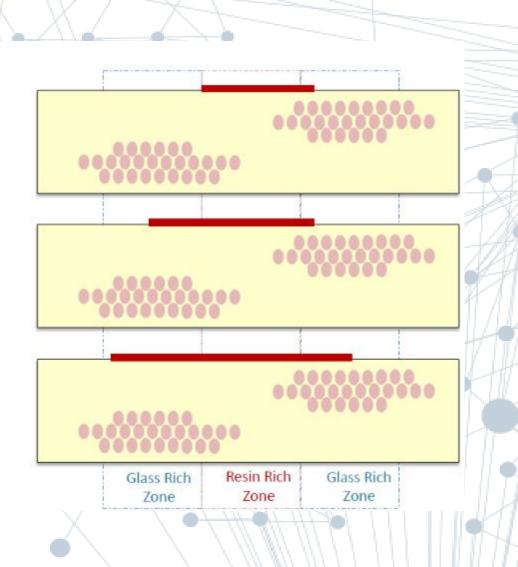

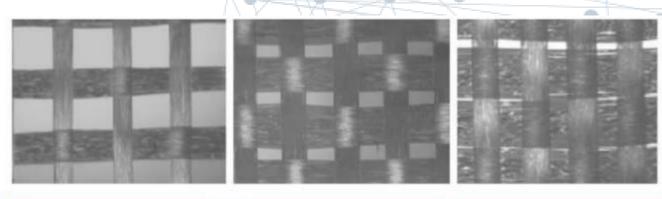

#### Glass style

- High variety of glass styles and resin contents available

- The resin content determins the Dk for a great deal

| Glass Style             | 7628          |

|-------------------------|---------------|

| Weight (grams/sq.m)     | 203           |

| Thread count            | 17.3 x 12.2   |

| Yarn (warp/weft)        | EC9 68/EC9 68 |

| Glass thickness (mm)    | 0.17          |

| Pressed thickness* (mm) | 0.18 - 0.22   |

|   | 2116          |

|---|---------------|

|   | 104           |

|   | 23.6 x 22.8   |

|   | EC7 22/EC7 22 |

| Ī | 0.095         |

|   | 0.110 - 0.125 |

|   |               |

| 2113          | 2125          |

|---------------|---------------|

| 78            | 87            |

| 23.6 x 22.0   | 15.7 x 15.4   |

| EC7 22/EC5 11 | EC7 22/EC9 34 |

| 0.079         | 0.09          |

| 0.085 - 0.10  | 0.10 - 0.12   |

| - 6   | 1080      |

|-------|-----------|

|       | 47        |

| 23.6  | 5 x 18.5  |

| EC5 1 | 1/EC5 11  |

| (     | 0.05      |

| 0.06  | 5 - 0.080 |

|     | 106         |

|-----|-------------|

|     | 24          |

| 22  | 2.0 x 22.0  |

| EC5 | 5.5/EC5 5.5 |

|     | 0.033       |

| 0.0 | 48 - 0.060  |

#### Glass style

Trace width effects on Skew

# Glass style

Spread glass

| Glass Style                | 106             |

|----------------------------|-----------------|

| Weight (grams/sq.m)        | 24              |

| Thread count               | 22.0 x 22.0     |

| Yarn (warp/weft)           | EC5 5.5/EC5 5.5 |

| Glass thickness (mm)       | 0.033           |

| Pressed thickness*<br>(mm) | 0.050 - 0.060   |

|   | 1067 Spread **  |

|---|-----------------|

|   | 31              |

|   | 27.6 x 27.6     |

|   | EC5 5.5/EC5 5.5 |

|   | 0.035           |

| П | 0.054 - 0.064   |

| Ш |                 |

#### Conclusion

- Before starting a design be aware of all your requirements

- Determine the material needed and check availability

- Do not over specify your design

- ➤ E.g. don't choose an ultra low loss material if you are only running on 5-10Ghz

- Consult Fineline-QPI for advise

# Thank you for your attention!

#### FINELINE QPI BV

The Dutch based Subsidiary of Fineline Global

Panovenweg 12 5708 HR Helmond The Netherlands

T +31 (0)492 590059 E INFO-QPI@FINELINE-GLOBAL.COM I FINELINE-GLOBAL.COM | QPIGROUP.COM

#### PCB

Single | Double sided

Multi-layer

Flex circuit

Flex-rigid circuit

Stretch circuits

IMS -  $Al_2O_3$  technology

#### Design

Mentor - PADS | Expedition | DX

Zuken – Cadstar

Altium – Designer

Cadence – Orcad | Allegro