# FPGA'S – THE DAWN OF A NEW ERA...

DAVID THOMAS - CHANNEL DIRECTOR INTEL PSG EMEA

## PLEASE DO REACH OUT - FIND US @ THE ARROW STAND

# **ACCELERATION WITH INTEL® FPGA'S**

# **FPGA OUTLOOK**

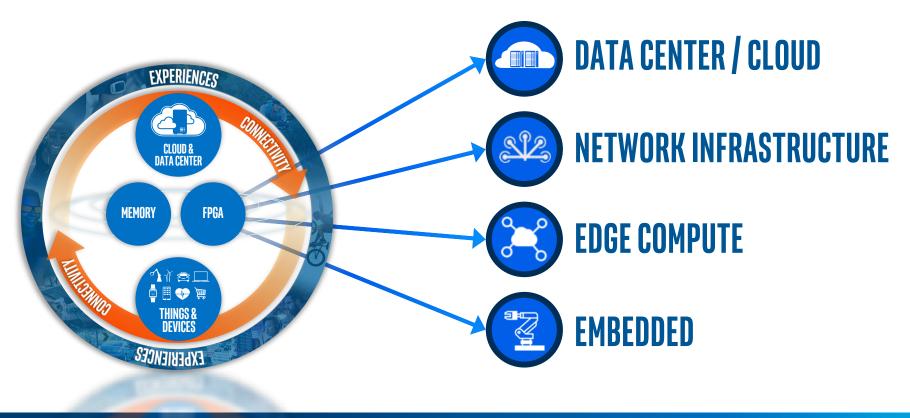

### INTEL® FPGA : APPLICATION ACCELERATION FROM EDGE TO CLOUD

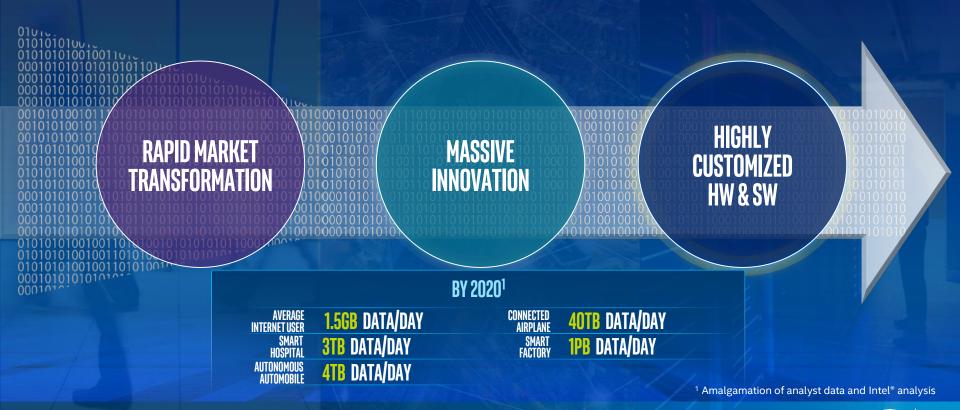

#### Massive Data Driving Market Change

intel

## **DATA CENTER CONSIDERATIONS**

#### Performance & Capabilities

Operations Per second

Low Latency

Scalability

Total Cost of Ownership **Compute Efficiency**

> Power Consumption

Utilization

🔄 Management

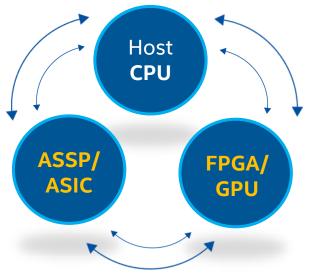

### **ACCELERATION CHOICES**

Acceleration of compute means HETEROGENEOUS COMPUTE

DEDICATED ACCELERATORS for maximum compute efficiency of specific, stable functions

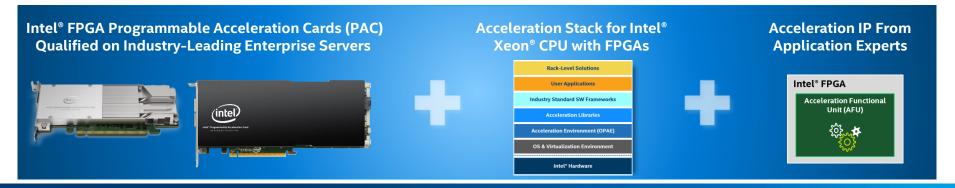

### **INTEL® FPGA PAC PRODUCTS SOLUTION FEATURES**

**SERVER QUALIFIED/VALIDATED FLEXIBLE HARDWARE**

Ð,

</>

LOW LATENCY, DETERMINISTIC, HIGH PERFORMANCE

HIGH ENERGY EFFICIENCY (PROCESSING/WATT)

**(☆→)** EASY DEVELOPMENT - OPENCL<sup>™</sup>, HLS, 3<sup>RD</sup> PARTY SOLUTIONS

**COMPREHENSIVE SOFTWARE SUPPORT – ORCHESTRATION TO SILICON**

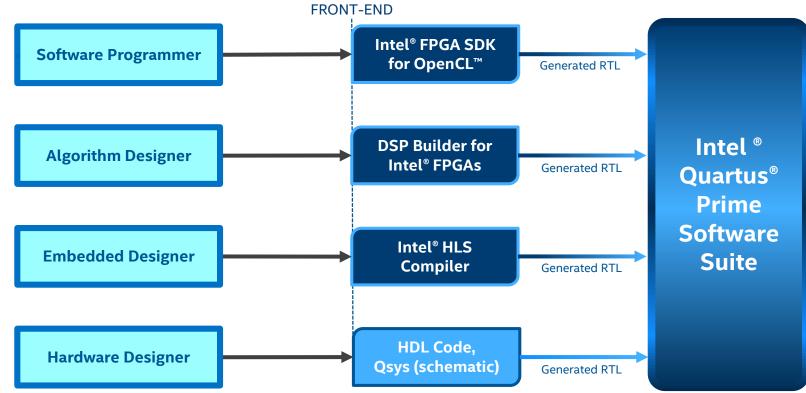

## **FPGA HIGH-LEVEL DESIGN TOOL PORTFOLIO**

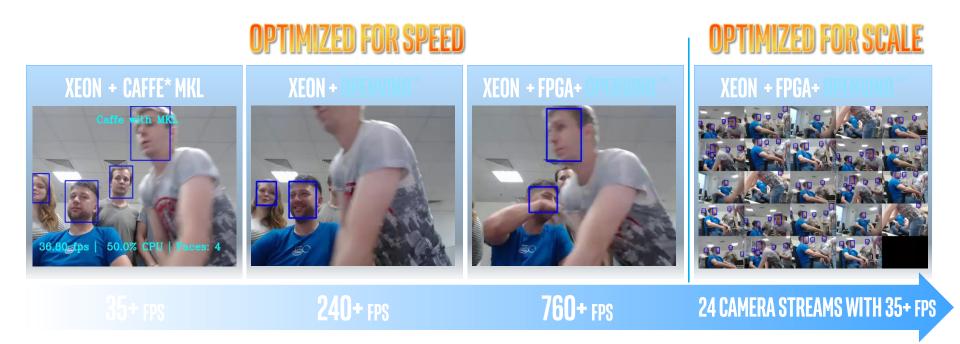

### **ACCELERATING DATA CENTER WORKLOADS**

#### Supercharge Datacenter Performance & Reduce TCO with the Versatility of Intel® FPGAs

### **INTEL WORKLOAD ACCELERATION SOLUTIONS – READY NOW!**

| <b>r</b> eniac                                | swarm64                                       | Computing                            |                            |                                                 | Levyx                                       | napatech                                        |

|-----------------------------------------------|-----------------------------------------------|--------------------------------------|----------------------------|-------------------------------------------------|---------------------------------------------|-------------------------------------------------|

| No SQL<br>Cassandra                           | Data<br>Warehousing                           | Genomics<br>GATK                     | JPEG2Lepton<br>JPEG2Webp   | Streaming<br>Analytics                          | Financial Black<br>Scholes                  | Network<br>Security/<br>Monitoring              |

| 6X<br>Performance                             | 4X+<br>Performance                            | 2.5X<br>Performance                  | 3-4X<br>Performance        | 5X<br>Performance                               | 8X<br>Performance                           | 3X<br>Performance                               |

| Deterministic<br>low latency at<br>higher Q/S | High Ingest<br>rate with fast<br>query/second | Speedup of<br>Broad GATK<br>pipeline | Transcode<br>images faster | Real-time AI<br>inference within<br>Spark BigDL | Risk Analytics<br>within Spark<br>framework | Deep Packet<br>Inspection at<br>40Gbps lossless |

| Est. 80% TCO<br>savings                       | Est. 50% TCO<br>savings                       | Est. 60% TCO<br>savings              | Est. 45% TCO<br>savings    | Est. 50% TCO<br>savings                         | Est. 50% TCO<br>savings                     | Est. 75% TCO<br>savings                         |

More on the way.....

11

### FPGA Edge Inference with OpenVino<sup>™</sup>

### SUPERCHARGE DATACENTER PERFORMANCE & LOWER TCO WITH THE VERSATILITY OF INTEL® FPGA

|                                                                                                                    | $\mathbf{Q}$                                                                                           |                                                                                                      |                                                                                             |

|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Performance                                                                                                        | Efficiency                                                                                             | Versatility                                                                                          | Ease of Use                                                                                 |

| <ul> <li>Programmable Hardware</li> <li>Programmable Software</li> <li>Low Latency &amp; High Bandwidth</li> </ul> | <ul> <li>Low Power through<br/>H/W specific accelerators</li> <li>Better Server Utilization</li> </ul> | <ul> <li>Choice of FPGA Platforms</li> <li>Growing Ecosystem of<br/>Accelerator Functions</li> </ul> | <ul> <li>Acceleration Stack</li> <li>Common User Interface</li> <li>IP Migration</li> </ul> |

| I/O                                                                                                                | (\$)                                                                                                   | 2023 A                                                                                               | jiii.                                                                                       |

| FASTER WORKLOAD<br>Acceleration                                                                                    | LOWER TOTAL<br>Cost of ownership                                                                       | ADAPT QUICKLY TO EVOLVING<br>Workloads & Standards                                                   | INCREASED<br>PRODUCTIVITY                                                                   |

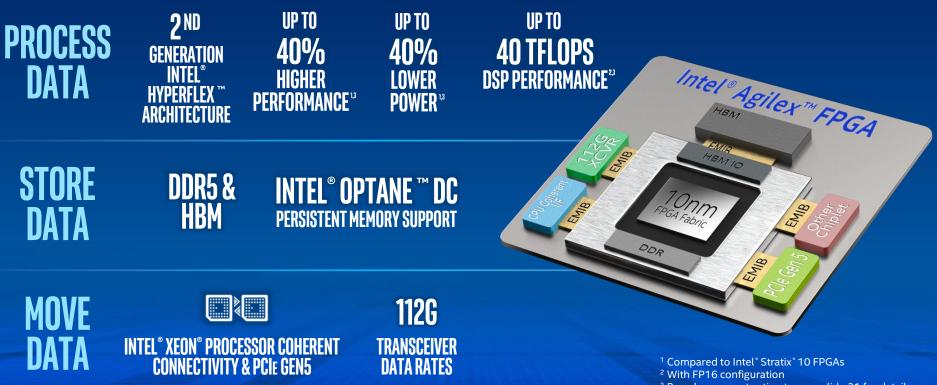

# INTRODUCING THE FPGA FOR THE DATA-CENTRIC WORLD

intel

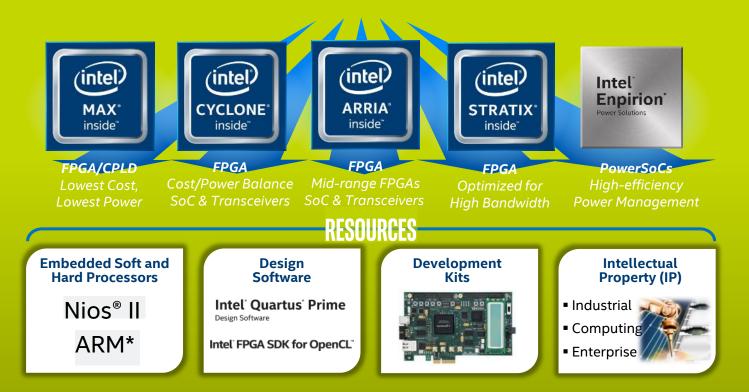

### **INNOVATION ACROSS THE BOARD**

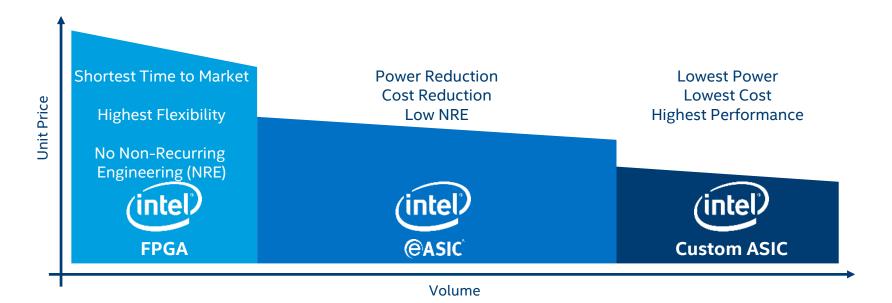

#### The Complete Custom Logic Portfolio

(intel)

### Agilex : The FPGA for the Data-Centric World

<sup>3</sup> Based on current estimates, see slide 21 for details

17

íntel

### Intel<sup>®</sup> Agilex<sup>™</sup> FPGA Tools for Developers

#### Hardware Developers

- Higher productivity:

- 30% improvement in compile times<sup>5</sup>

- New productivity flows and usability features for faster design convergence

- Higher efficiency: 15% improvement in memory utilization<sup>5</sup>

#### Software Developers

- Single source, heterogenous programming environment

- Support for common performance library APIs

- FPGA support with Intel software development tools including Intel<sup>®</sup> VTune<sup>™</sup> Amplifier & Intel<sup>®</sup> Advisor

<sup>5</sup>See slide 21 for details

## **ONE API**

### **LEGAL DISCLAIMERS**

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration. No computer system can be absolutely secure. Check with your system manufacturer or retailer or learn more at intel.com.

Tests document performance of components on a particular test, in specific systems. Differences in hardware, software, or configuration will affect actual performance. Consult other sources of information to evaluate performance as you consider your purchase. For more complete information about performance and benchmark results, visit <a href="http://www.intel.com/performance">http://www.intel.com/performance</a>.

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products. For more complete information visit <a href="http://www.intel.com/performance">http://www.intel.com/performance</a>.

Cost reduction scenarios described are intended as examples of how a given Intel-based product, in the specified circumstances and configurations, may affect future costs and provide cost savings. Circumstances will vary. Intel does not guarantee any costs or cost reduction.

This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest forecast, schedule, specifications and roadmaps.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

Statements in this document that refer to Intel's plans and expectations for the quarter, the year, and the future, are forward-looking statements that involve a number of risks and uncertainties. A detailed discussion of the factors that could affect Intel's results and plans is included in Intel's SEC filings, including the annual report on Form 10-K.

All products, computer systems, dates and figures specified are preliminary based on current expectations, and are subject to change without notice. The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel does not control or audit third-party benchmark data or the web sites referenced in this document. You should visit the referenced web site and confirm whether referenced data are accurate.

© Intel Corporation. Intel, the Intel logo, the Intel Inside mark and logo, Arria, Cyclone, Intel Xeon, MAX, Quartus and Stratix are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries.

\*Other marks and brands may be claimed as the property of others.Intel Corporation. Intel, the Intel logo, and others are trademarks of Intel Corporation in the U.S. and/or other countries.

Altera, Arria, Cyclone, Enpirion, Max, Megcore, Nios, Quartus and Stratix, words and logos are trademarks of Altera and registered in the U.S. Patent and Trademark Office and in other countries.

\*Other names and brands may be claimed as the property of others.

### IN BEHALF OF INTEL AND ARROW TEAM

Programmable Solutions Group