# On the Evolution of Qualification Methods and Standards for Microelectronics in Automotive Applications beyond AEC-Qxx

NXP – René Rongen

29 NOVEMBER 2018 TECHNIEKHUYS VELDHOVEN PLOT CONFERENTIE TOMORROW'S RELIABILITY

### **Company Introduction**

#### PLOT CONFERENTIE 29 NOVEMBER 2018 TECHNIEKHUYS - VELDHOVEN

René Rongen / PLOT Conference 2018

## **Personal Introduction**

- Fellow / Corporate Q&R

- Joined NXP/ Philips as Reliability Engineer in 1997

- Internal Standardization

- NXP Reliability Policy

- NXP Cu-wire Way-of-Working

- External Standardization & Industry Consortia: Active participation in JEDEC, AEC, ZVEI

- Reliability "R&D", Competence Building, Knowledge Sharing

- NXP: Applied Reliability Training, Reliability Knowledge Framework

- Conferences: IRPS, ECTC, ESREF, AEC-RW / (co)author, session chair, invited speaker

- Dutch Accreditation Council: ISO17025 certification of reliability labs

- Problem Solving & Risk Assessments

- 1. Industry Trend & Evolution of Reliability Qualification Methods

- 2. AEC Automotive Electronic Council: Background

- 3. Automotive Electronics Reliability Challenge 1: Extended Testing & Mission Profiles

- 4. Automotive Electronics Reliability Challenge 2: Interaction with Applications / PCBs

- 5. Summary

- 1. Industry Trend & Evolution of Reliability Qualification Methods

- 2. AEC Automotive Electronic Council: Background

- **3.** Automotive Electronics Reliability Challenge 1: Extended Testing & Mission Profiles

- 4. Automotive Electronics Reliability Challenge 2: Interaction with Applications / PCBs

- 5. Summary

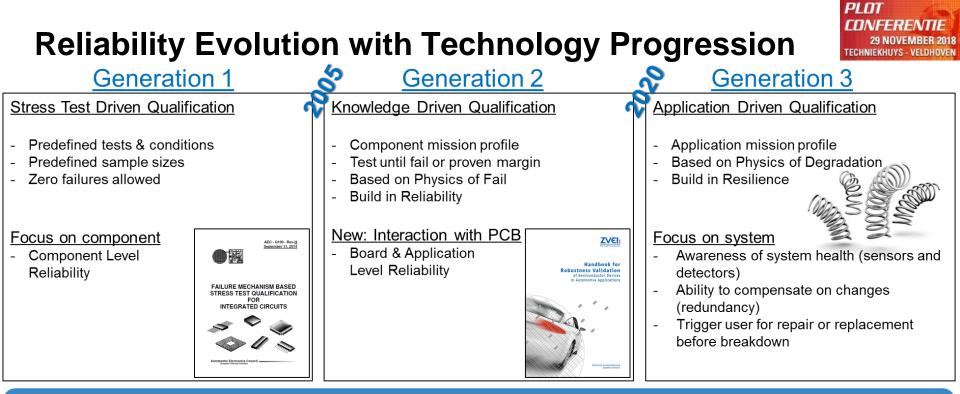

## **Industry - Trend**

- New technologies and application areas require in-depth knowledge on failure mechanisms and mission profiles

- Sensor and Radar application, ADAS, Autonomous Driving

- Automotive high temperature applications (beyond Q100 grade 0)

- Applications with extended operational life time e.g., charging of electric cars

- Industry standards and consortia move towards knowledge based qualification

- AEC Q100 and other AEC specs

- JESD94/ JEP122

- ZVEI Robustness Validation Handbooks

Automotive Electronics Council Component Technical Committee

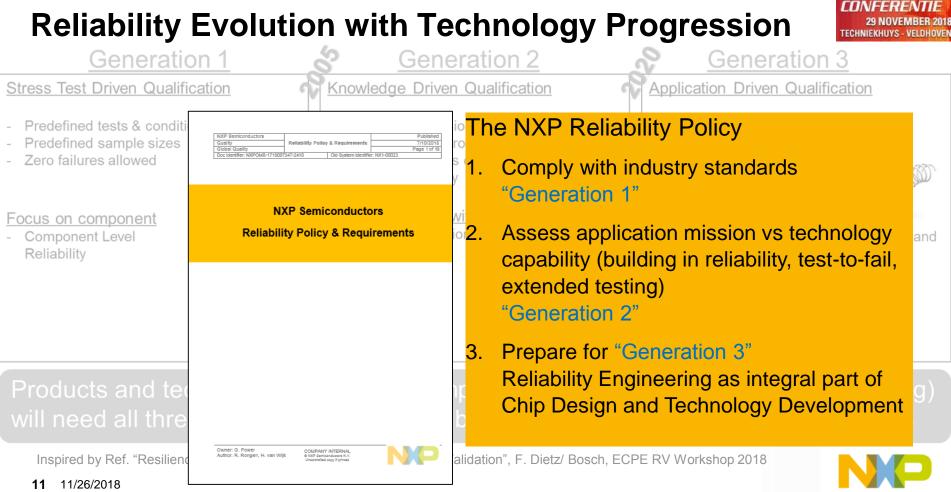

Products and technologies for future complex applications (IoT, Autonomous Driving) will need all three methods in an optimal balance to meet all reliability requirements

#### Reliability engineering after RV What is needed to implement a resilient system?

- 1. Sensors and detectors

- Standardized IP

11/26/2018

- Application-specific sensors

- Using an existing AD

- 2. Resilience core and communication interface

- 3. Ideally: integrated alternate operation modes

Goal is, that sensors, detectors and resilience core can re-use existing circuit blocks to minimize additional expenditure within the system!

Automative Electronica | AE/EIMI-Dir | January 25th, 2018 © Robert Bach Grabit 2017. All rights reserved, also regarding any disponal, exploitation, reproduction, editing, distribution, as well as in the event of applications for industrial property rights. BOSCH

PLOT

CONFERENTIE

**TECHNIEKHUYS - VELDHOVEN**

**29 NOVEMBER 2018**

Ref. "Resilience, Reliability Engineering after Robustness Validation", F. Dietz/ Bosch, ECPE RV Workshop 2018

Application Standardized Out Out Test specific degradation sensors sensors Sensors Analog circuitry Resilience Core DC-DC VDD, VB converter Slack monitors NVM Comm. Interface Event, degradation and margin-data Alternate mode configuration

#### PLOT CONFERENTIE 29 NOVEMBER 2018 TECHNIEKHUYS - VELDHOVEN

# How to shorten qualification times

- · Go extreme with test conditions :

- Correlation with standard test condition

- Reliability models

- · Unexpected and undesired failures

- Virtual qualification

- Material characterization

- · Failure mechanisms models

- Multi-discipline modelling

9 11/26/2018

Ref. "Workshop Automotive Challenges", C.M. Villa/ ST, ESREF 2018

#### Key Messages / Summary

Changes to come to the industry

- New automotive grades / classes will be defined in order to increase design freedom, but keep risk control

- ▶ *T*-grades

- A-grades Application (performance vs reliability) grades

- L-grades Lifetime grades, ...

- New automotive grades / classes will on the other hand force designers to stay in associated design limits which is not the case, today

- Design for compatibility is the answer to reliability & obsolescence management

- > This includes the usage of standardized MPs

- Replacement electronics approaches will come security licenses will have update limitations

- Function before car design cost efficient reliability assurance of electronics will achieve new ranks w.r.t. other car design aspects

- Joint technology forecasting, monitoring & road mapping along the supply chain is necessary and possible with proposed Platform

#### Automotive' is in the phase to be defined and renewed

PLOT

*TENTIE*

**TECHNIEKHUYS - VELDHOVEN**

ER 2018

10 11/26 Ref. "New Automotive Semiconductor Categories and Classes for Standardized Mission Profile Enablement - a through the supply chain alignment activity", A. Aal/ VW, 1<sup>st</sup> European AEC-RW Workshop 2018

PLM

René Rongen / PLOT Conference 2018

- 1. Industry Trend & Evolution of Reliability Qualification Methods

- 2. AEC Automotive Electronic Council: Background

- 3. Automotive Electronics Reliability Challenge 1: Extended Testing & Mission Profiles

- 4. Automotive Electronics Reliability Challenge 2: Interaction with Applications / PCBs

- 5. Summary

# **Automotive Electronics Council - AEC**

#### **Component Technical Committee**

- 1. Founded 1993, by a.o. Bob Knoell (chair until Sept 2018)

- 2. Original membership of 15 companies

- 3. Now at

- 18 Sustaining members

- 46 Technical Committee member companies

- 9 Associate member companies

- 4. ~ 35 spec/guidelines

- 5. Working Relationship with JEDEC, ESDA, JEITA, IEC, IPC

PIM

TECHNIEKHUYS - VELDHOVEN

### AEC: Standards under Revision or Preparation 2018

PLOT CONFERENTIE 29 NOVEMBER 2018 TECHNIEKHUYS - VELDHOVEN

| EC std #            | Current | AFC standard title                                                                              | AEC std #                                           | Current |                                                                                 |  |  |

|---------------------|---------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------|---------------------------------------------------------------------------------|--|--|

|                     | nev     |                                                                                                 |                                                     | Rev     | AEC standard duc                                                                |  |  |

| Q100                | H1      | Failure Mechanism Based Stress Test Qualification of integrated<br>Circuits (reference to Q006) | Q200                                                | E       | Stress Test Qualification for Passive Components                                |  |  |

| Q100-001            | 6       | Wire Bond Shear Test                                                                            | Q200-001                                            | A       | Elame Retardance                                                                |  |  |

| Q100-002            | D       | Human Body Model Electrostatic Discharge Test                                                   | Q200-002                                            | A       | Human Body Model Electrostatic Discharge Test                                   |  |  |

| <del>Q100-003</del> | Đ       | Machine Model Electrostatic Discharge Test                                                      | Q200-003                                            | A       | Beam Load (Break Strength) Test                                                 |  |  |

| Q100-004            | С       | IC Latch-Up Test                                                                                | Q200-004 0 Measurement Methods for Resettable Fuses |         |                                                                                 |  |  |

| 0100-005            | D       | Non-Volatile Memory Program/Erase Endurance, Data Retention                                     | Q200-005                                            | 0       | Board Flex / Terminal Bond Strength Test                                        |  |  |

|                     |         | and Operating Life Test                                                                         | Q200-006                                            | A       | Terminal Strength Surface Mount / Shear Strength Than                           |  |  |

| <del>Q100-006</del> | Ð       | Electrothermally-Induced Parasitic Gate leakage Test (GL)                                       | Q200-007                                            | 0       | Voltage Surge Test                                                              |  |  |

| Q100-007            | В       | Fault Simulation and Fault Grading                                                              |                                                     |         |                                                                                 |  |  |

| Q100-008            | A       | Early Life Failure Rate (ELFR)                                                                  | Q001 D Parts Average Testing                        |         |                                                                                 |  |  |

| Q100-009            | В       | Electrical Distributions Assessment                                                             | Q002                                                | В       | Statistical Yield Analysis<br>Guide for Characterization of Integrated Lincuity |  |  |

| Q100-010            | A       | Solder Ball Shear Test                                                                          | Q003                                                | U       |                                                                                 |  |  |

| Q100-011            | С       | Charged Device Model (CDM) Electrostatic Discharge Test                                         | Q004                                                | A       | Zero Defects Guideline (unreleased)                                             |  |  |

| Q100-012            |         | Short Circuit Reliability Characterization of Smart Power Devices for                           | Q005                                                | В       | Pb-Free Test Requirements                                                       |  |  |

|                     |         | 12V Systems                                                                                     | Q006                                                | A       | Copper Wire Qualification                                                       |  |  |

| Q101                | E       | Stress Test Qualification for Discrete Semiconductors                                           | Charter                                             | A       | AEC Charter                                                                     |  |  |

| Q101-001            | A       | Human Body Model (HBM) Electrostatic Discharge (ESD) Test                                       | Q104                                                | 0       | MCM/Module Qualification                                                        |  |  |

| Q101-002            | A       | Machine Model (MM) Electrostatic Discharge (ESD) Test                                           |                                                     |         | PC Board Qualification                                                          |  |  |

| Q101-003            | A       | Wire Bond Shear Test                                                                            | Q103                                                | 0       | MEMS / Sensors                                                                  |  |  |

| Q101-004            | 0       | Miscellaneous Test Methods                                                                      | Q102                                                | 0       | LED                                                                             |  |  |

| Q101-005            | 0       | Capacitive Discharge Model (CDM) Electrostatic Discharge (ESD)<br>Test                          | Q100 Rev. I                                         | 1       | Bare Die/KGD                                                                    |  |  |

| 0101-005            |         | Short Circuit Reliability Characterization of Smart Power Devices for                           |                                                     | 0       | Touch Systems                                                                   |  |  |

| Q101-006            | 0       | 12V Systems                                                                                     |                                                     |         | System Level ESD                                                                |  |  |

- 1. Industry Trend & Evolution of Reliability Qualification Methods

- 2. AEC Automotive Electronic Council: Background

- 3. Automotive Electronics Reliability Challenge 1: Extended Testing & Mission Profiles

- 4. Automotive Electronics Reliability Challenge 2: Interaction with Applications / PCBs

- 5. Summary

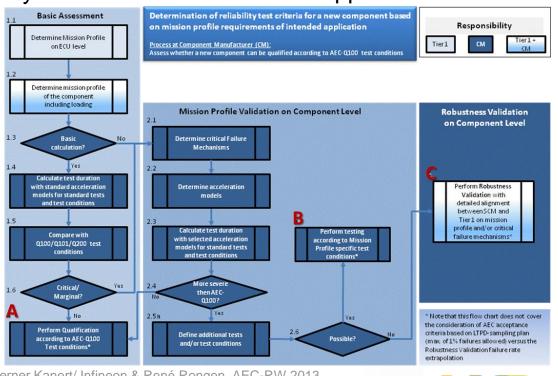

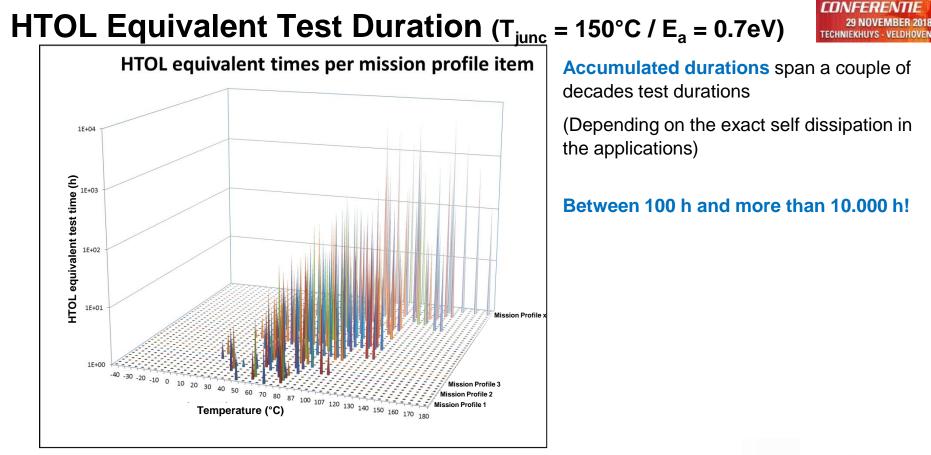

## **Automotive Electronics Reliability: Challenge 1**

AEC-Q100 needs to provide clarity: Extended test durations, AND Standardized Mission Profiles

Tier1s and OEMs have to accept

Explanation to flow chart:

- A AEC Q100 Standard Qualification

- B Extended Qualification based on Customer Specific MP

- C Modeling / test-to-fail based validation

Ref .:

- 1. AEC-Q100H Appendix 7

- 2. "Robustness Validation an Introductory Tutorial". Werner Kanert/ Infineon & René Rongen, AEC-RW 2013

- 3. "Extended Lifetime Qualification based on Standard Mission Profiles", Ulrich Abelein/ Infineon, AEC-RW 2018

**16** 11/26/2018

#### "AEC-Q100/101 - Appendix 7"

PLOT

CONFERENTIE

29 NOVEMBER 2018 TECHNIEKHUYS - VELDHOVEN

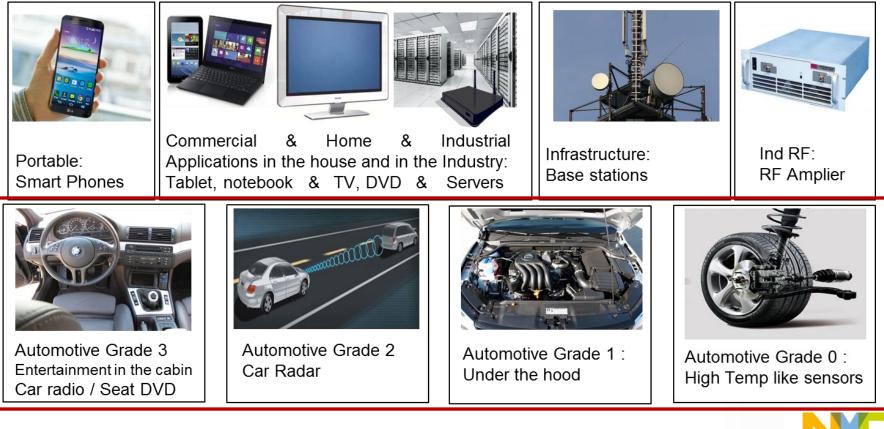

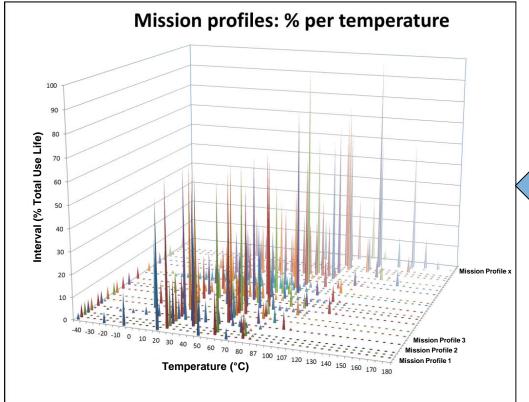

## NXP's "Generic" Mission Profiles; 4 for Automotive

PLOT

CONFERENTIE

29 NOVEMBER 2018 TECHNIEKHUYS - VELDHOVEN

### Analysis of > 40 Automotive Mission Profiles ...

Note: Obviously there is more to cover than only 4 AEC-Q100 Grades...

Table 1: Part Operating Temperature Grades

PLOT

29 NOVEMBER 2018 TECHNIEKHUYS - VELDHOVEN

|        | Grade    | Ambient Operating Temperature Range |

|--------|----------|-------------------------------------|

|        | <u>0</u> | <u>-40°C to +150°C</u>              |

|        | 1        | -40°C to +125°C                     |

| $\neg$ | <u>2</u> | -40°C to +105°C                     |

|        | <u>3</u> | -40°C to +85°C                      |

Courtesy: Fred Kuper, Internal NXP Report 2014

PLOT

Courtesy: Fred Kuper, Internal NXP Report 2014

### What is the Limit? Or Failure vs Degradation or Change...

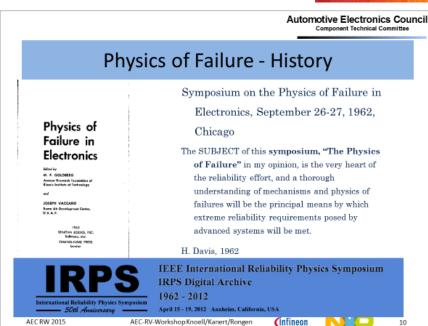

- <u>Physics-of-Fail (PoF)</u>:

- Principle is already as old as Semiconductor Industry

- It is all about understanding processes and mechanisms causing degradation with eventual failure of materials and components

- Testing until fail can take a long time...

- And if failures occur...

Still the failure mechanism to be understood!

- Alternatively, the process of degradation after "time zero" can be recorded:

- Physics-of Degradation (PoD) or even better Physics-of-Change (PoC)

PLOT CONFERENTIE 29 NOVEMBER 2018 TECHNIEKHUYS - VELDHOVEN

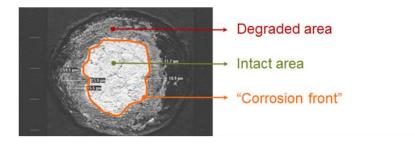

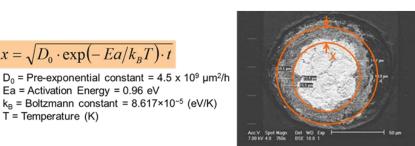

## Example of PoD: High T Corrosion for Cu-wire

Dynamics of Cu-Al Intermetallic Compound (IMC) Corrosion at high T:

IMC analysis method <sup>1</sup>: remove Cu-ball & mold compound in fuming nitric acid and analyze left ٠ intermetallic layer with back scatter SEM analysis

Model of Degradation <sup>2</sup>:

$x = \sqrt{D_0 \cdot \exp(-Ea/k_B T) \cdot t}$

Ea = Activation Energy = 0.96 eV

T = Temperature (K)

$k_{\rm P}$  = Boltzmann constant = 8.617×10<sup>-5</sup> (eV/K)

#### References:

- G.M. O'Halloran, et al., "Planar Analysis of Copper-Aluminium Intermetallics", in Proc. International Symposium for testing and Failure Analysis (ISTFA), San Jose, CA, Nov 3-7 2013, pp.297-300

- Lifetime prediction of Cu-Al wire bonded contacts for different mold compounds, R. Rongen et al., Electronic Components and Technology Conference, ECTC 64th, 2014, pp 411-418

#### Model allows life time prediction of the contact WITHOUT reliability test 11/26/2018

PLOT

CONFERENTIE

**29 NOVEMBER 2018 TECHNIEKHUYS - VELDHOVEN**

21

- 1. Industry Trend & Evolution of Reliability Qualification Methods

- 2. AEC Automotive Electronic Council: Background

- 3. Automotive Electronics Reliability Challenge 1: Extended Testing & Mission Profiles

- 4. Automotive Electronics Reliability Challenge 2: Interaction with Applications / PCBs

- 5. Summary

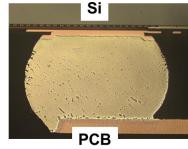

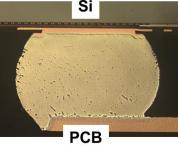

## **Automotive Electronics Reliability: Challenge 2**

AEC-Qxx:

No standard test method nor requirements for Board Level/ Electrical Solder Joint Reliability Currently: only user (Tier1) specific methods and requirements - very inefficient...

In addition: ٠

> The "interaction" between 1<sup>st</sup> level (component level) and 2<sup>nd</sup> level (board level) reliability Currently: only <u>guidelines</u> in JEP150

level of assembly: solder joint reliability

Second level reliability or board level reliability

First level reliability

Attachment of a component to the next

Corrosion

Thermomechanical

PIM

Wafer Level Packages:

Is it 1<sup>st</sup> or 2<sup>nd</sup> level?

TECHNIEKHUYS - VELDHOVEN

#### Bumped Dies: New Approach (Flip Chip, Fan-out WLP and WL CSP)

- Two key differences compared to conventional plastic packages

- Failure modes accelerated by TC are different: dominant are cracks in the BEoL

These can only be accelerated in the presence of a solder connection (see next slide)

- Handling WLCSP may results in (many) non-stress related fails

Mounting on a carrier is effectively preventing damage due to handling

- In principle JEP150 does apply in this case (assembled solid state devices); the problem is that JEP150 is not giving any requirements

- NXP defined test method & requirements internally

- Guidelines (no requirements) added to latest JESD47 revision K (IC Qualification Standard for Commercial & Industrial Application)

- Major OEM for mobile applications adjusted its IC Qualification Standard accordingly

- Will AEC-Qxx be next?

#### Flip Chip, Fan-out WLP and WL CSP Thermomechanical Failure Modes in BEoL

| ТС Туре                               | Test vehicle                                           |  | Electrical signature | Phy                  | vsical signature  |

|---------------------------------------|--------------------------------------------------------|--|----------------------|----------------------|-------------------|

| Component Level<br>(CL-TC)            | Singulated<br>functional devices<br>or part of a wafer |  | No failure           | No damage<br>(crack) |                   |

| Board Level<br>( <b>BL-TC</b> )       | Daisy chains on a<br>PCB carrier                       |  | No failure           | Damage<br>(crack)    |                   |

| Application Level<br>( <b>AL-TC</b> ) | Functional devices<br>on a PCB carrier                 |  | Failure              | Damage<br>(crack)    | confirmed by FEM) |

Ref.: Reliability of Wafer Level Chip Scale Packages, R. Rongen, R. Roucou, P.J. vd Wel, F. Voogt, F. Swartjes, K. Weide-Zaage, Microelectronics Reliability, 2014, Volume 54, pages 1988-1994

#### **25** 11/26/2018

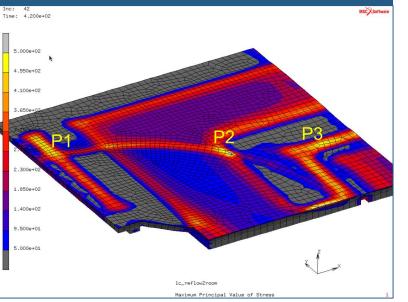

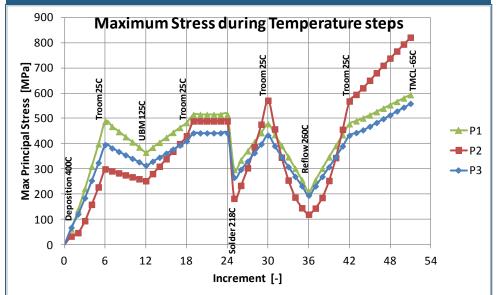

#### Flip Chip, Fan-out WLP and WL CSP Example BEoL Stress Modeling for WL CSP

# P1, P2 and P3: relevant metal structures in the corner of the die

Modeling of principal stress development over time: bumping – PCB soldering – AL-TC

#### Modeling allows for setting up design rules

**26** 11/26/2018

#### Flip Chip, Fan-out WLP and WL CSP Background NXP AL TC Requirements

Taking 1000 c from -40 to 85 °C as reference and using Coffin-Manson (CM) equation with exponent 6 for the other conditions:

| 1   | Low T | High T | Reference | Calculated  | *Coffin-Manson equation:                                                                                        |

|-----|-------|--------|-----------|-------------|-----------------------------------------------------------------------------------------------------------------|

| - 5 | (°C)  | (°C)   | (C)       | (C)*        | $(\Lambda T, )^{n}$                                                                                             |

|     | -40   | 85     | 1000      | <u>1000</u> | $AF = \frac{\Delta T_{stress}}{\Delta T}$                                                                       |

|     | -40   | 125    |           | 189         | $\left(\Delta I_{use}\right)$                                                                                   |

|     |       |        |           |             | AFAcceleration FactorΔT <sub>atress</sub> Temperature swing during stress testΔTuseTemperature swing during use |

CM exponent 6 is selected because the failure mode to cover is not solder joint fatigue but crack in the <u>BEoL</u>.

n = 6

CM exponent; brittle fractures (JEP122)

To ensure robustness margin while not breaking solder joints, NXP uses 300 c from -40 to 125 °C as a requirement for AL TC, ~ 1.5 x 189 c (*blue-italic*), for non automotive .

For Automotive, AL TC requirements range from 500 to 1000 c

- 1. Industry Trend & Evolution of Reliability Qualification Methods

- 2. AEC Automotive Electronic Council: Background

- **3.** Automotive Electronics Reliability Challenge 1: Extended Testing & Mission Profiles

- 4. Automotive Electronics Reliability Challenge 2: Interaction with Applications / PCBs

#### 5. Summary

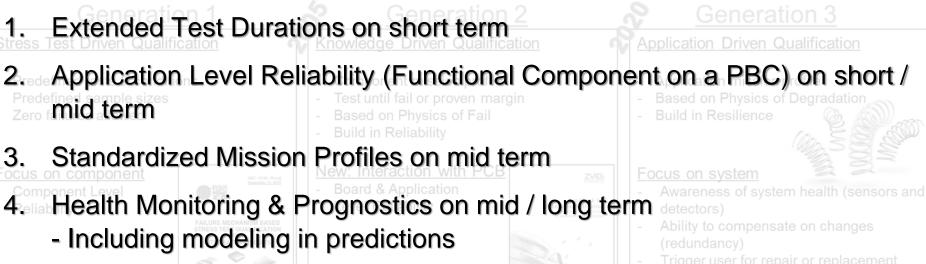

## **Qualification Method Evolution beyond AEC-Qxx**

PIM

TECHNIEKHUYS - VELDHOVEI

- 5. "Virtual" qualifications (using modeling) will not replace but complement "real" qualifications on mid / long term

- Boundary Condition: industry wide exchange of Knowledge on Physics of Fail / Degradation / Change

# **Contact Details**

- NXP Semiconductors

- Gerstweg 2, 6534 AE Nijmegen BX0.035

- +31 (0)6 51 17 1461

- rene.rongen@nxp.com

29 NOVEMBER 2018 TECHNIEKHUYS VELDHOVEN PLOT CONFERENTIE TOMORROW'S RELIABILITY