BRIDGING THE GAP BETWEEN CAD & CAM

#### PCB Design Flow

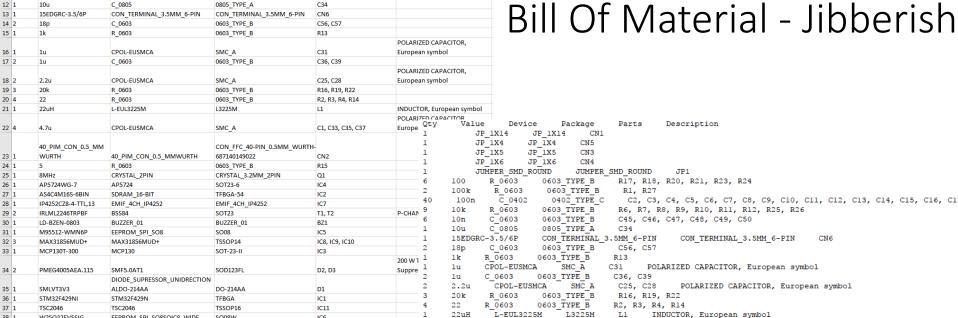

Defining your BOM (Bill Of Material)

**Create Schematics**

Size the PCB and Place Key Components

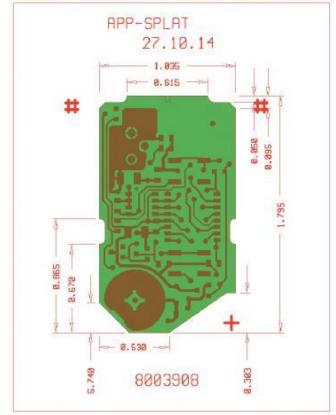

Make the PCB Layout

Export data from CAD for manufacturing

# TOP DFM ISSUES Bare Board

- CAD data not readable

- CAD data not complete

- Ambiguity between CAD data and included info files

- Ambiguity between CAD data and online chosen order details

- Ambiguity in the CAD data

- More than 1 contour

- Layer conventions

- Mixing Imperial and Metric units

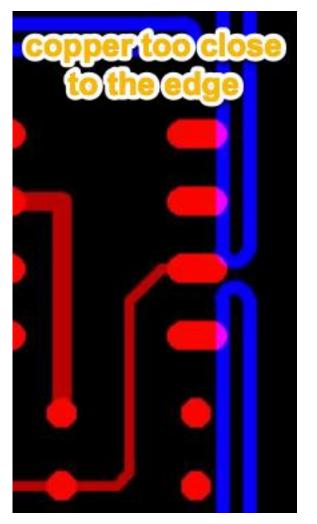

- Copper to close to the edge or to routing

- Routing and contour issues

- Open tracks

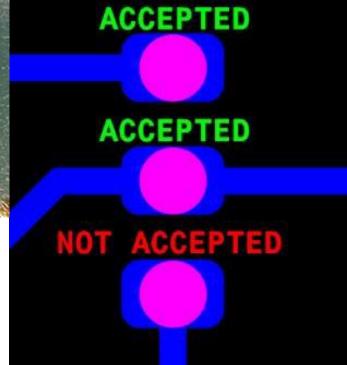

- Annular ring problems

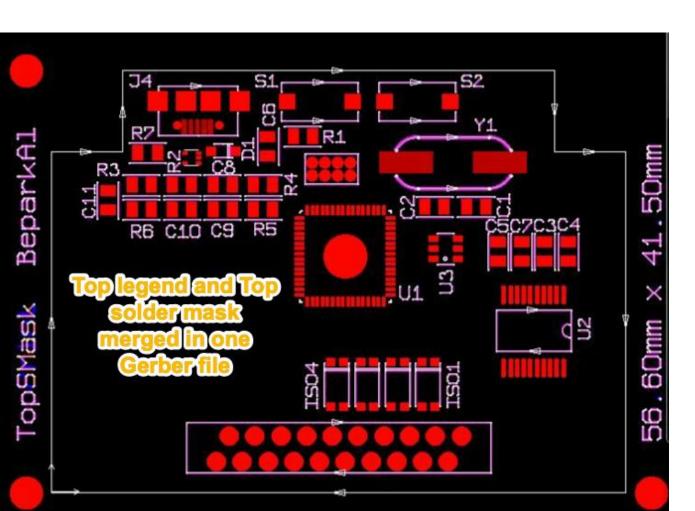

- Ambiguities in the Solder Mask

- Exposed copper

- Covered solder pads

- DRC violations in general

- Plating index not OK

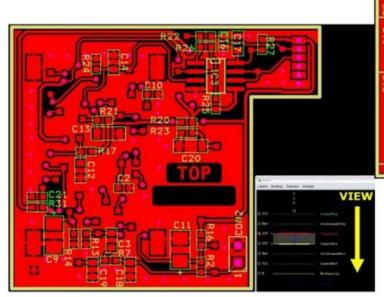

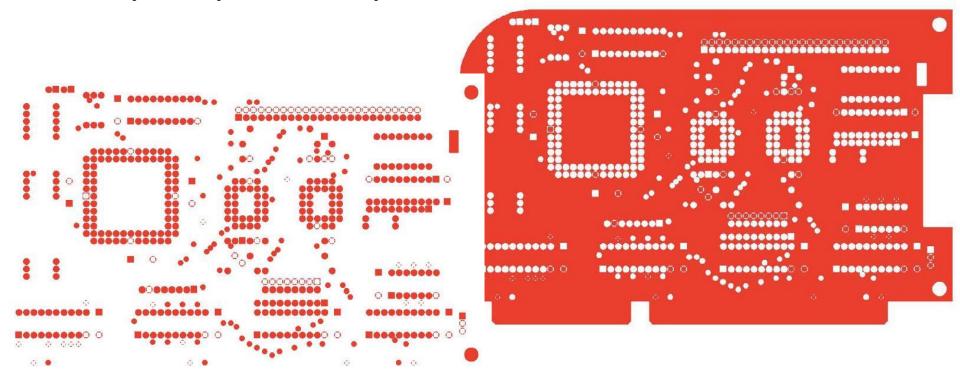

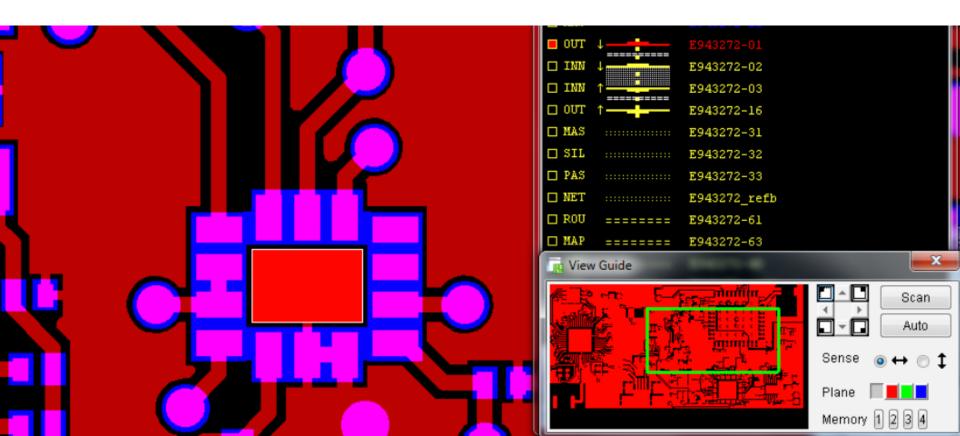

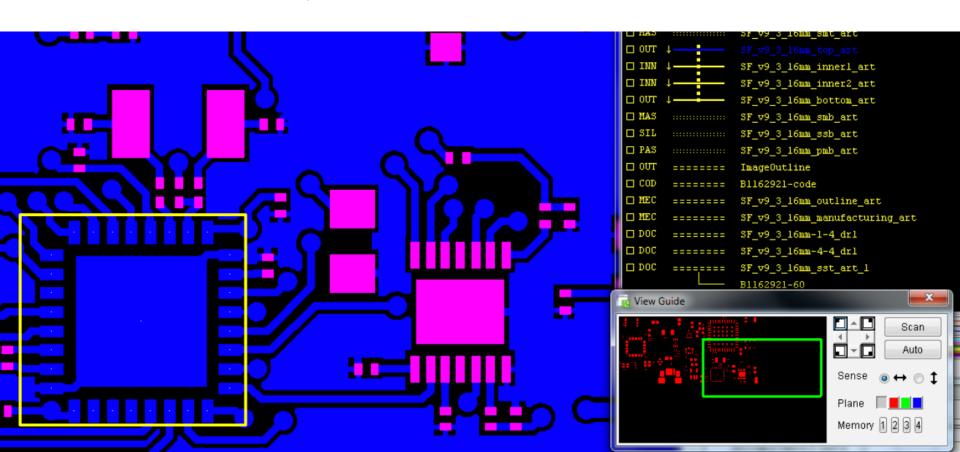

### All layers ALWAYS viewed from the TOP

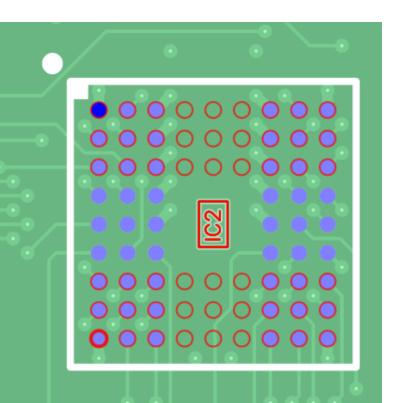

## Drills versus copper pads

Same Unit -Resolution

WORLD OF TECHNOLOGY & SCIENCE

Centered

Different Unit - Resolution

Non Centered

# Layer polarity matters

Bad output generated from CAD

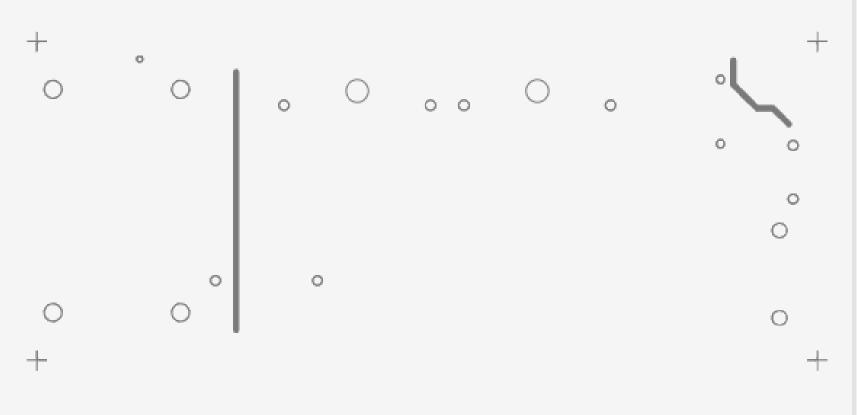

### Bad outline

### Data outside the PCB contour

WWW.WOTS.NL

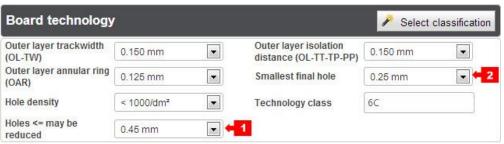

Not respecting the design rules

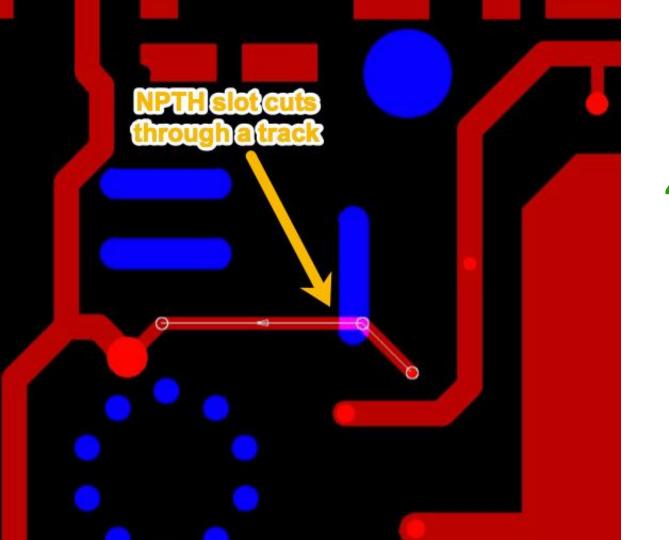

"track cut through"

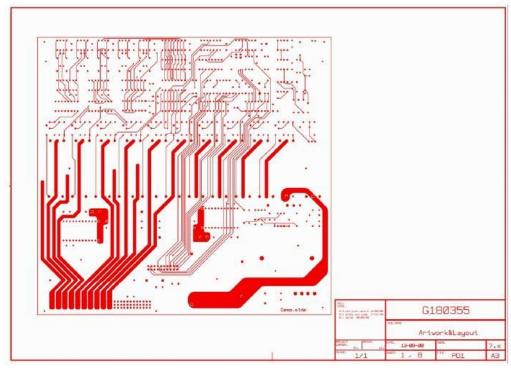

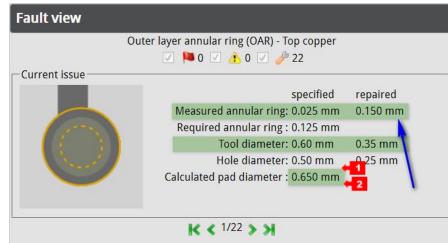

# annular ring issues

AR = (Pad D - Tool D) / 2 (Tool D = D drill bit) Faulty AR = (0.650 mm - 0.60 mm) / 2 = 0.025 mmRepaired AR = (0.650 mm - 0.35 mm) / 2 = 0.150 mm

### Soldermask issues

## Solder paste issues

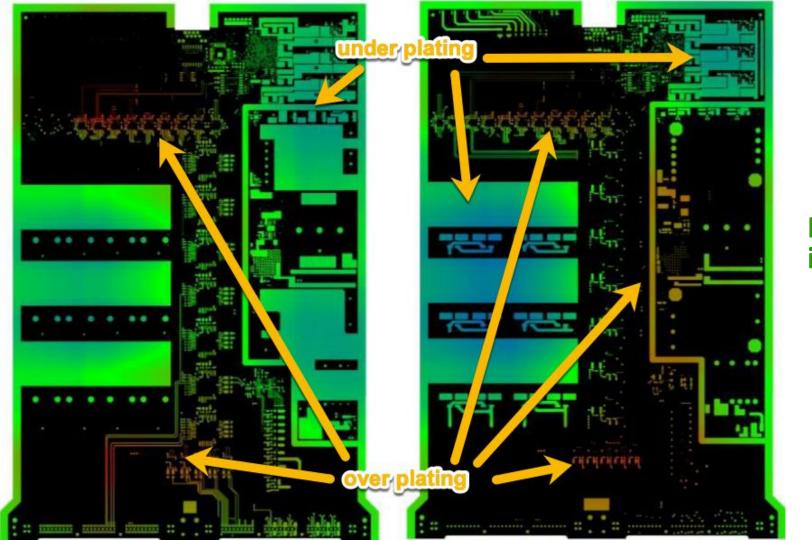

## PCB production issues

NPTH: 0.15mm on toolsize (0.15mm on endsize)

PTH - Same net : 0.15mm on toolsize (0.25mm on endsize)

PTH - Diff net: 0.25mm on toolsize (0.35mm on endsize)

Plating issues

# TOP DFM ISSUES assembly

- Solder escapes

- Cold spot Hot spot

- Copper unbalanced per comp (tomb stoning)

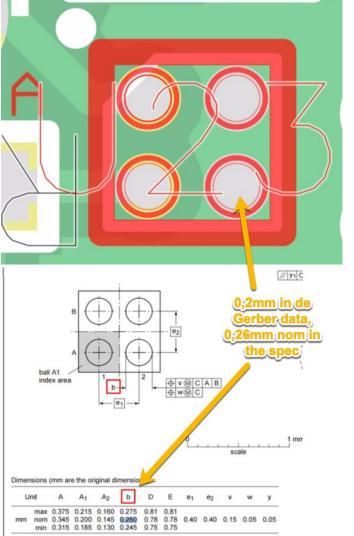

- Pad sizes <-> geometry component

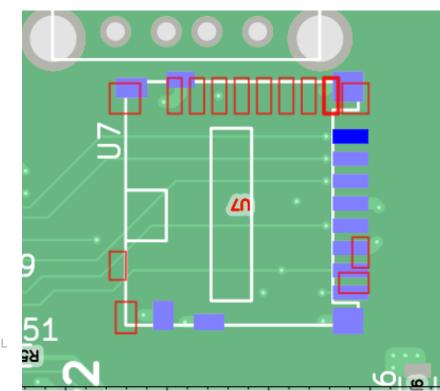

- Footprint: component vs PCB

- Rotation

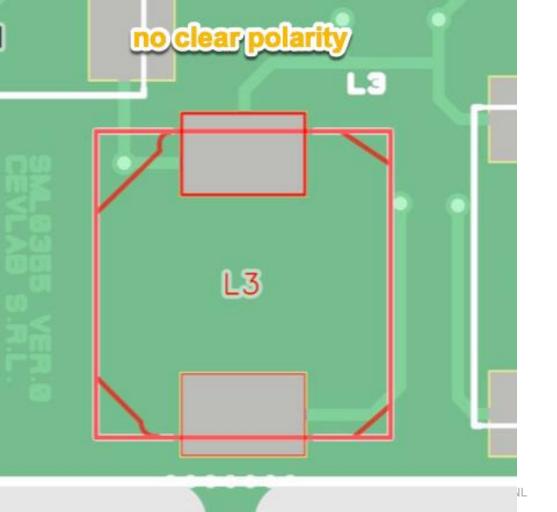

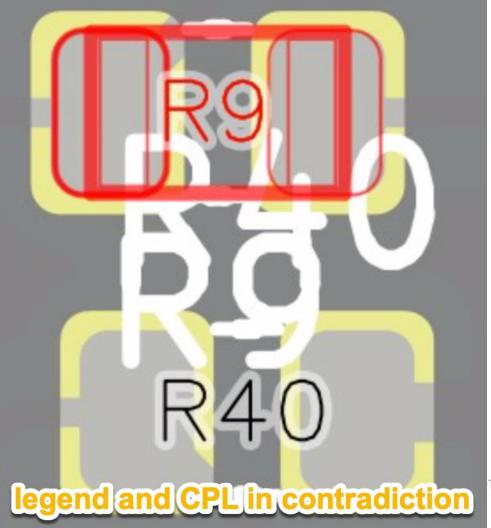

- Pin1 + polarity

- Solder mask problems -Bridges not manufacturable etc...

- BGA QFN LGA <= 0.5 mm</li>

-> finish Che Ni/Au or Ag

- Via in pad -> adapt layout or Via filling or No Go

- Fiducials?

- Panel

- PCB

- Component

- Overhanging components?

- V-Cut

- Break bridges

- Panel border width

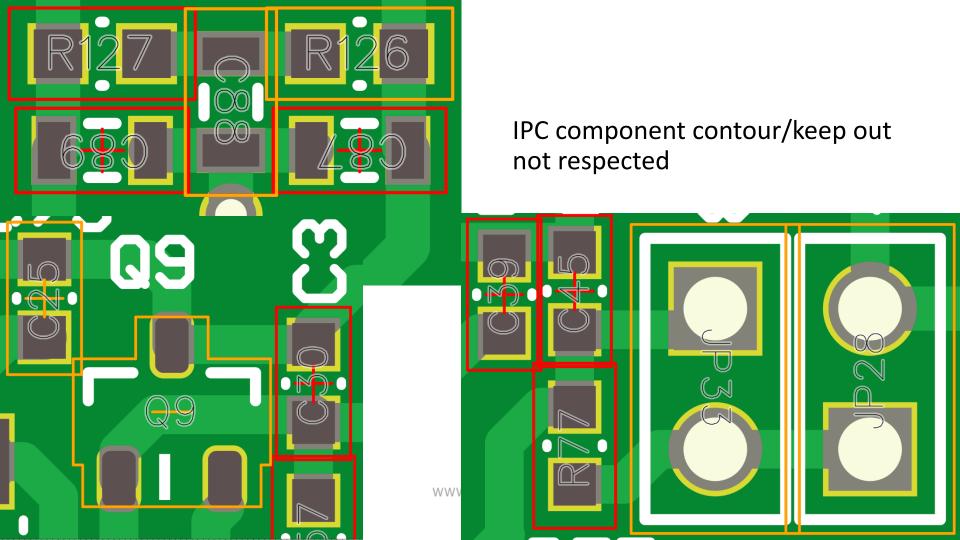

- IPC component clearance

R6, R7, R8, R9, R10, R11

R12, R25, R26 C45, C46, C47, C48, C49

C50

#### W25Q32FVSSIG EEPROM SPI SOSSOICS WIDE

& SCIENCE

R 0603

C 0603

Different file formats used BOM output from CAD system is limited -

0603 TYPE B

0603 TYPE B

Cryptic description of component and package LD-BZEN-0803 WORLD OF TECHNOLOGY

10 9

10k

10n

C1, C33, C35, C37

EMIF 4CH IP4252

IC8, IC9, IC10

40 PIM CON 0.5 MMWURTH

TFBGA-54

T1. T2

IC3

BZ1

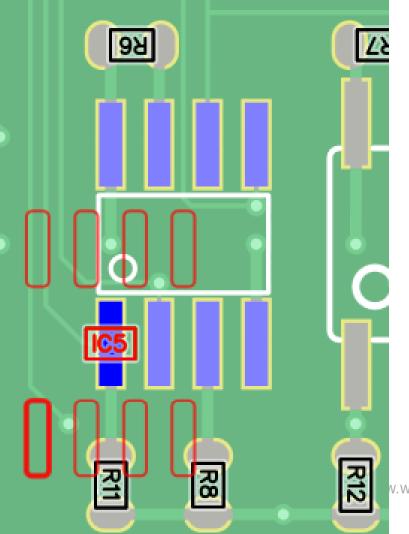

IC5

R15

CRYSTAL 3.2MM 2PIN

BUZZER 01

SOT-23-II

DIODE SUPRESSOR UNIDRECTIONALDO-214AA

TFBGA

5008

SOD123FL

IC11

TSSOP14

0603 TYPE B

BUZZER 01

MCP130

SDRAM 16-BIT

EEPROM SPI SO8

SMF5.0AT1

TSSOP16

EEPROM SPI SO8SOIC8 WIDE

MAX31856MUD+

CRYSTAL 2PIN

AS4C4M16S-6BIN

MAX31856MUD+

MCP130T-300

W25032FVSSIG

SMLVT3V3 STM32F429NI

PMEG4005AEA.115

POLARIZED CAPACITOR, European symbol

Transient Voltage Suppressor

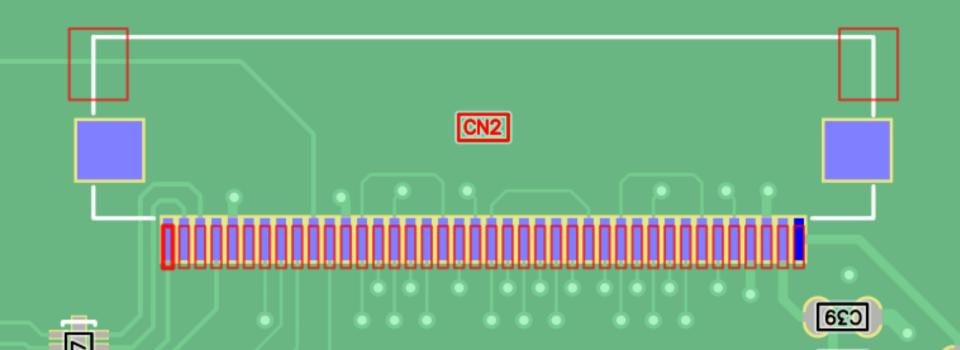

CN2

CON FFC 40-PIN 0.5MM WURTH-687140149022

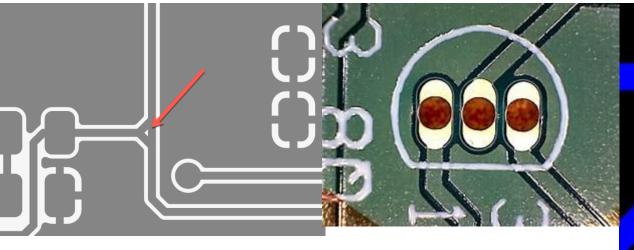

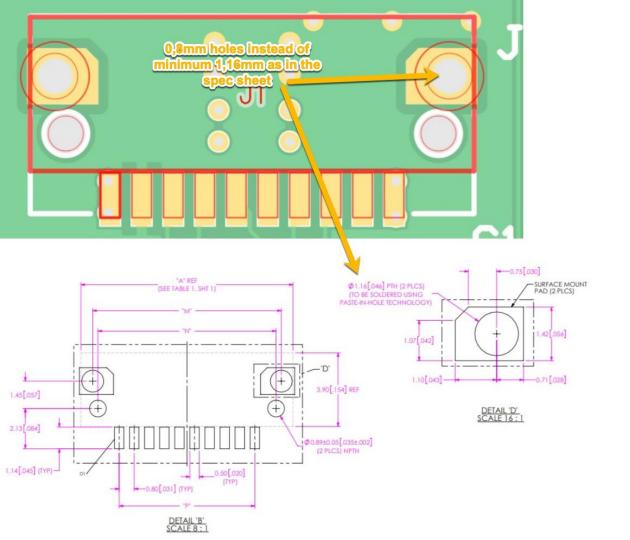

Component specs not respected in the PCB layout

Component specs not respected in the PCB layout

- Footprint check CAD-info against other database

- Incorrect component chosen. Same device available with different packages

- Incorrect footprint definition in CAD library

- Location

- PIN1 vs centroid location in Component Placement List file

W.WOTS.NL

- Rotation

- Each library can define its own default rotation

- CAD ERP Machine

WWW.WOTS.NL

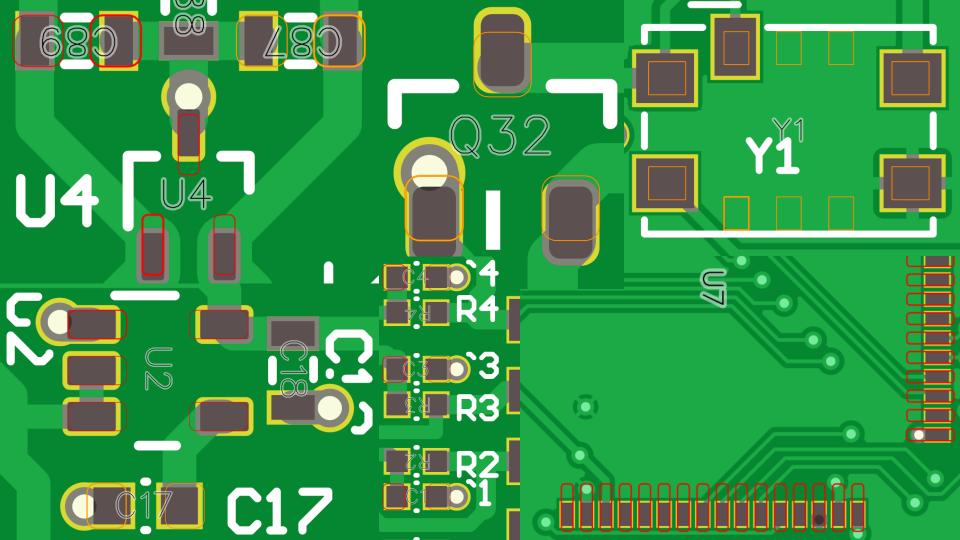

No polarity indication between Component Placement List and Gerber data

Contradictory

data in

Component

Placement List

and legend

(Gerber data)

TS.NL

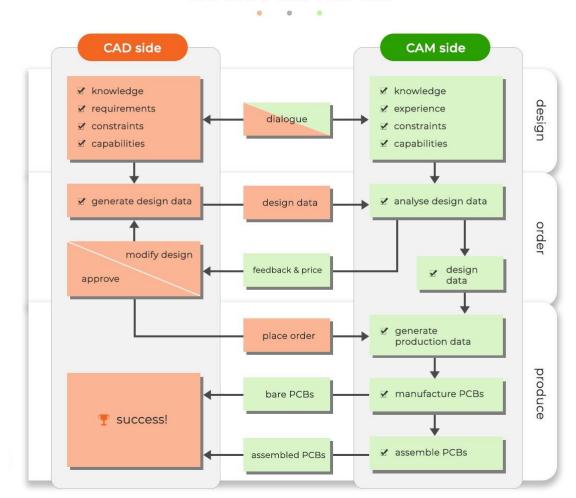

#### CAD to CAM

optimum PCB design flow

01

**First Think**

02

**Then Act**

03

Achieve "Right First Time"

- •In time

- •On Budget

#### —— BRIDGING THE GAP ——

BETWEEN CAD AND CAM

Virtual production of your electronics

How?

# CIRCUITS

- Your board "right first time"

- on time

- accurate to your intentions

- at best total cost

- Thanks

- Visit us at booth 9C090

Who are we?

- Prototypes & Small Series, produced & assembled in house

- Almost 100% of our sales = online

- 2022 figures:

- +/- 500 Eurocircuits colleagues

- + 12.000 professional customers (20.000 users) in Europe

- + 110.000 orders

- +/-40 M€ consolidated sales

- Started 1991, is Belgian and is privately owned

- Factories in Hungary and Germany & Engineering in India

- Local sales in Belgium (HQ), France, Germany, UK,

Switzerland, Italy, Spain and Hungary