Kort samengevat kunnen we zeggen dat High-Level Synthese (HLS), een ontwerpproces is dat een gedrags- of algoritme beschrijving van een ontwerp omzet in digitale hardware. High-Level Synthese gaat uit van een hoger abstractie niveau, met andere woorden ontwerp details hoeven nog niet gespecificeerd te worden. Grotere OEM’ers maken gebruik van deze technologie maar de spreker van Core|Vision verwacht dat dit binnen enkele jaren ook interessant is voor kleinere ontwikkelteams.

Kort samengevat kunnen we zeggen dat High-Level Synthese (HLS), een ontwerpproces is dat een gedrags- of algoritme beschrijving van een ontwerp omzet in digitale hardware. High-Level Synthese gaat uit van een hoger abstractie niveau, met andere woorden ontwerp details hoeven nog niet gespecificeerd te worden. Grotere OEM’ers maken gebruik van deze technologie maar de spreker van Core|Vision verwacht dat dit binnen enkele jaren ook interessant is voor kleinere ontwikkelteams.

Als voorbeeld nemen we een FIR filter. De ontwerper hoeft alleen het algoritme te beschrijven en zich geen zorgen te maken over timing zaken, latency , coëffiënten en data samples opslag etc. Doel is focussen op het algoritme, deze simuleren en verifiëren. Hardware realisatie is voor latere zorg. Met behulp van verschillende implementatie algoritmes kan de beste oplossing gekozen worden. De nadruk van HLS ligt op algoritme ontwikkeling en niet meer op de hardware implementatie. Tijdens het D&E Event geeft Core|Vision een lezing over het gebruik van HLS voor FPGA design.

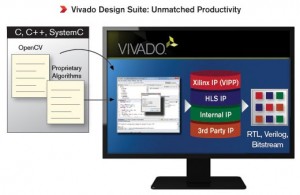

VHDL is de hardware-taal voor FPGA ontwikkeling. De nieuwste generatie Xilinx SoC FPGAs heeft ARM processoren en diverse IP blokken die moet worden gecontroleerd en geconfigureerd via een op software gebaseerde aanpak. C / C ++ of SystemC worden nu gebruikt als de nieuwe hardware taal voor SoC FPGA’s. Met Vivado High-Level Synthese, wordt C-code omgezet in een FPGA netlist. Frank de Bont demonstreert stap voor stap hoe dit proces werkt.

Low-Power FPGA Video and Image Processing Solutions

Low-Power FPGA Video and Image Processing Solutions FPGA Pin Optimization

FPGA Pin Optimization Speed-up Your FPGA-on-Board Design Flow

Speed-up Your FPGA-on-Board Design Flow PolarFire FPGA-Based Solution

PolarFire FPGA-Based Solution