By Kenneth Wyatt, courtesy of Interference Technology.

By Kenneth Wyatt, courtesy of Interference Technology.

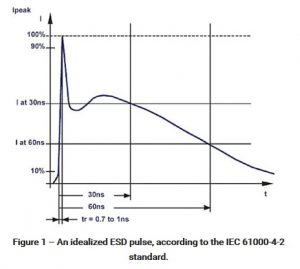

One issue I see fairly often with unshielded consumer or commercial products is CPU resets during periods of immunity testing, such as during electrostatic discharge (ESD) testing. Untreated, this can lead to field failures and associated customer satisfaction issues. The remedy is usually quite simple and IC manufacturers even mention the solution, but it’s usually buried deep within the data sheet. That is, an R-C low pass filter. Figure 1 shows a simplified depiction of an ESD waveform (from the IEC 61000-4-2 standard). ESD current pulses will typically have rise times much less than 1 ns.

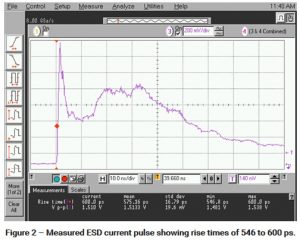

As measured using just a 1.5 GHz bandwidth oscilloscope, the mean rise time was measured at 575 ps, as shown in Figure 2. It’s obviously bandwidth-limited, as I’ve measured rise times as fast as 35 ps on some very fast oscilloscopes.

As measured using just a 1.5 GHz bandwidth oscilloscope, the mean rise time was measured at 575 ps, as shown in Figure 2. It’s obviously bandwidth-limited, as I’ve measured rise times as fast as 35 ps on some very fast oscilloscopes.

One client of mine was having quite a challenge with ESD tripping the CPU reset of their embedded processor. The board they were using was a general purpose one with many I/O connectors arranged around the edges. Merely connecting a USB cable would reset the processor. Even the ESD generated by people walking by, would cause a rest to occur.

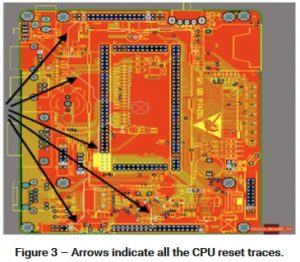

I examined the PC board layout and have drawn in arrows showing how the CPU reset signal traces are leading out to all the connectors and crisscross the board over several inches (Figure 3). Of course, these long reset traces served as quite good receive antennas and easily coupled the ESD fields into the CPU.

I examined the PC board layout and have drawn in arrows showing how the CPU reset signal traces are leading out to all the connectors and crisscross the board over several inches (Figure 3). Of course, these long reset traces served as quite good receive antennas and easily coupled the ESD fields into the CPU.

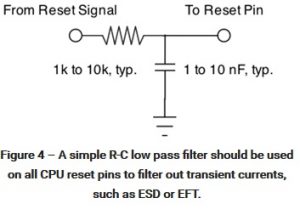

As mentioned, the solutions is a simple R-C low pass filter. The values are not critical and typically, the resistor might be 1k to 10k Ohms and the capacitor, 1 to 10 nF (Figure 4).

For more information on testing and troubleshooting ESD effects on ICs, we have a special guest speaker, Sven König, from Langer EMV-Technik GmbH, who will be presenting a free webinar, ESD and Efficient Electronic Design Finding and Fixing Problems at the IC Level, at the 2017 EMC Live series, April 25 through 27.

For more information on testing and troubleshooting ESD effects on ICs, we have a special guest speaker, Sven König, from Langer EMV-Technik GmbH, who will be presenting a free webinar, ESD and Efficient Electronic Design Finding and Fixing Problems at the IC Level, at the 2017 EMC Live series, April 25 through 27.

In this webinar we will discuss the impact of IC behavior on electronic design, specifically the characteristics of ESD and how they influence a device by influencing the ICs. To identify ESD problems, a special test setup must be used to recreate the disturbance at the IC level during the design process. This will save the engineer developing time and effort. Some ESD problems will be explained and supplemented by a practical example at both the electronic and IC level.

Registration for this worldwide event will open in early March, so look for the announcement shortly. If your company is interested in presenting an EMC-related topic please find details here.

22 april Distinguished Lectures...

22 april Distinguished Lectures... Deelname aan de schaduwcommissie...

Deelname aan de schaduwcommissie...